# UNIT-I

# **DEFINITIONS FOR DIGITAL SIGNALS**

### **Analog versus Digital**

- Electronic circuits and systems can be conveniently divided into two broad categories generally referred to as *analog* and *digital*.

- Analog circuits, designed for use with small signals, can be made to work in a linear fashion. An operational amplifier (op amp) connected as an amplifier with a voltage gain of 10 is an analog circuit.

- The output voltage for this circuit will be faithfully amplified version of any signal presented at its input till saturation is reached. This is *linear operation*.

- > Digital circuits are generally used with *large signals* and are considered nonlinear.

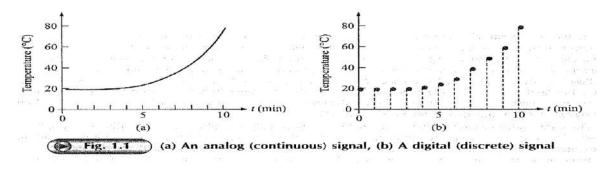

- Any quantity that changes with time either can be represented as an analog signal or it can be treated as a digital signal.

- For example, place a container of water at room temperature on a stove and apply heat. The measurable quantity of interest here is the change in water temperature. The temperature is recorded *continuously*, and it changes smoothly from 20°C to 80°C.

- While being heated, the water temperature passes through every possible value between 20°C and 80°C. This is an example signal of an analog.

- In this case, the recorded temperature is *not* continuous. Rather, it *jumps* from point to point, and there are only a finite number of values between 20°C and 80°C say, at an increment of 1°C like 20°C, 21 °C, 22°C, and so on. There are exactly 11 values in this case.

- When a quantity is recorded as a series of distinct (discrete) points, it is said to be *sampled*.

This is an example of a digital signal.

1

Digital signals represent only a finite number of discrete values, Digital circuits and systems can used be to process both analog signals and digital signals.

# **Binary System**

- Digital electronics today involves circuits that have exactly two possible states. A system having only two states is said to be binary (*bi* means "two").

- The *binary number system* has exactly two symbols----0 and 1. The binary number system is used in digital electronics. Electronic circuit can be described in terms of its voltage levels.

- ▷ Digital circuit, there are only two The more positive voltage is the *high (HJ* level, and the other is the *low (L)* level. This is immediately related to the binary number system by assigning L = 0 and H = 1.

- Many functions performed by digital circuits are *logical operations*, and thus the terms true(T)

| Decimal  | Binary | Decimal  | Binary |

|----------|--------|----------|--------|

| <b>0</b> | 0000   | 8        | 1000   |

| 1        | 0001   | 9        | 1001   |

| 2        | 0010   | 10       | 1010   |

| 3        | 0011   | 11       | 1011   |

| 4        | 0100   | 12       | 1100   |

| 5        | 0101   | 13       | 1101   |

| 6        | 0110   | 14       | 1110   |

| 7        | 0111   | 15 15 IS | 1111   |

and false (*F*) are often used. Choosing H = 1 = T and L = 0 = F is called *positive logic*.

- The majority of digital systems utilize positive logic. Note it that is also possible to construct a *negative logic* system by choosing H = .0 = F and L = 1 = T.

- Today the majority of digital circuit families utilize a single +5 Vdc power supply, and the two voltage levels used are +5 Vdc and O Vdc. Here is a summary of the two binary states (levels) in this positive logic system.

+5 V de =

$$H = I = T$$

0Vdc = $L=0=F$

- You can no doubt see how to extend these definitions to include terms such as on-off go-no go, yes-no, and so on.

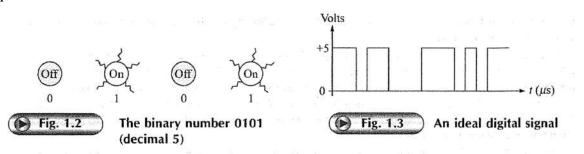

- A lamp or a *light-emitting* diode (LED) is frequently used to indicate digital signal. On (illuminated) represents 1, and off(extinguished) represents 0.

➤ As an example, the four LEDs in Fig. 1.2 are indicating the binary number 0101, which is equivalent to decimal 5.

# **Ideal Digital Signals**

The voltage levels in an *ideal* digital circuit will have values of either + 5 V de or O V de. Furthermore, when the voltages change (switch) between values, they do so in zero time

# **DIGITAL WAVEFORMS**

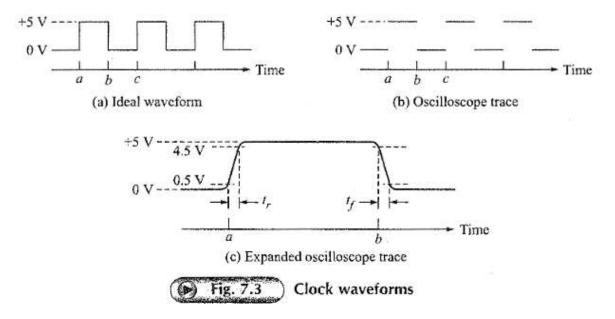

The ideal digital signal represented in Fig. 1.3 has two precise voltage levels-+ 5 V de and OV de. Furthermore, the signal switches from one level to the other in zero time. In reality, modern digital circuits can produce signals that approach, but do not quite attain, this ideal behavior.

## **Voltage levels**

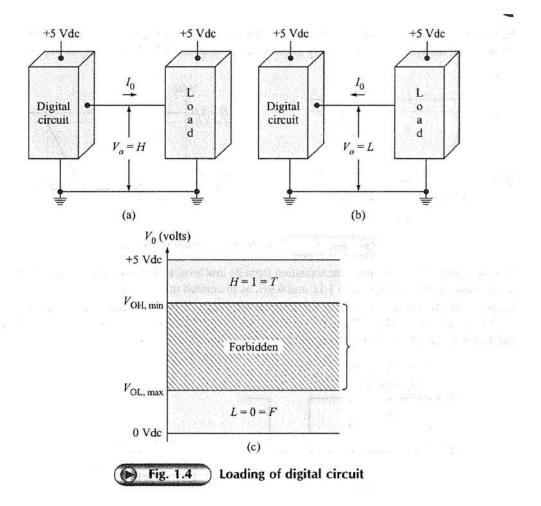

- First of all, the output voltage level of any digital circuit depends somewhat on its load, as illustrated in Fig. 1.4a below. When  $V_0$  is high, the voltage should be +5 Vdc.

- In this case, the digital circuit must act as a *current source* to deliver the current 1 to the load. However, the circuit may not be capable of delivering the necessary current 1 while maintaining +5 V de.

- To account for this, it is agreed that any output voltage close to +5 Vdc within a certain range will be considered high. This is illustrated in Fig. 1.4c, where any output voltage level between +5 V de and V H,min is defined as H = 1 = T. The term V B,min stands for the minimum value of the output voltage when high.

- As we will see, one popular transistor-transistor logic (TTL) family of digital circuits allows  $V_0$ H,min = +3.5 Vdc. In this case, any voltage level between +5 Vdc and +3.5 Vdc is H= 1.

- > In Fig. 1.4b. $v_0$  is low, and the digital circuit must act as a *current sink*. That is, it must be capable of accepting a current  $I_0$  from the load and delivering it to ground. In this situation, ~, should be 0 Vdc, but the

and  $V_0$  L,max' is defined as L = 0 = F. The term  $V_0$  L,max stands for the *maximum* value of the output voltage when low.

Again, the popular TTL family mentioned above allows  $V_0$  L,max = +0.1 Vdc. Thus, any voltage level between +0.1 Vdc and O Vdc is L = 0.

# **Switching Time**

- If the digital circuit were *ideal*, it would change from high to low, or from low to high, in zero time.

- Thus, the output voltage would never have a value in the forbidden range. In reality, it does, in fact, require a finite amount of time for V to make the transition (switch) between levels.

- > The time required for  $V_0$ , to make the transition from its high level to its low level is defined as *fall time t*,.

- > For ease of measurement, it is customary to measure fall time using 0.9H and 1. IL.

- The time required for  $V_0$  to make the transition from its low level to its high level is defined as *rise time t*,...Again, rise time is measured between 1.1 L and 0.9H.

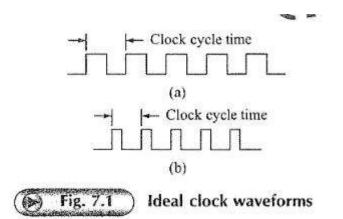

#### **Period and Frequency**

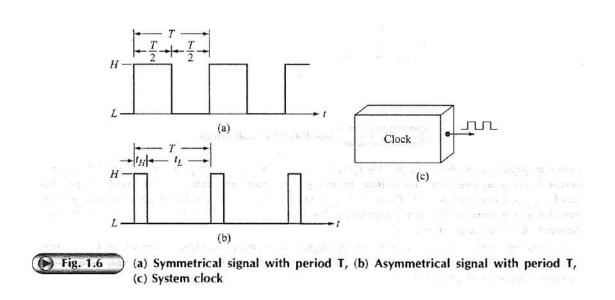

- > There are many occasions where a symmetrical digital signal will be used (clock and counter circuits for instance). The period T of this waveform is shown: This is the time over which the signal repeats itself.

- A rectangular waveform such as this can be produced by adding together an infinite (or at least a large number) of sinusoidal waveforms of different frequencies and amplitudes.

- Even though this digital signal is not sinusoidal, it is convenient to define the frequency as/= 1/T. As an example, if the period of this square wave is I µs, then its frequency is found as

$$f = \frac{1}{T} = \frac{1}{1 \,\mu s} = \frac{1}{10^{-6}} = 10^6 = 1 \text{ MHz}$$

- A symmetrical signal is frequently used as the basis for timing all operations in a digital system. As such, it is called the *clock signal*.

- > The electronic circuit used to generate this square wave is referred to as the *system clock*.

- A system clock is simply an oscillator circuit having a very precise frequency. Frequency stability is provided by using a crystal as the frequency-determining element.

# **Duty Cycle**

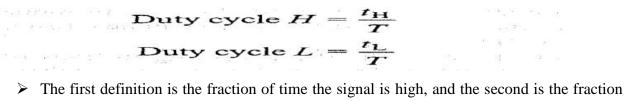

Duty cycle is a convenient measure of how symmetrical or how unsymmetrical a waveform is. For the waveform there are two possible definitions for duty cycle.

- of time the signal is low. Either definition is acceptable, provided you clearly define which you are using. To express as a percentage, simply multiply by 100.

- > Note that the duty cycle for a syletrical wave

Duty cycle H = Duty cycle  $L = \frac{T/2}{T} = 0.5$  or (50%)

# **DIGITAL LOGIC**

## **Generating Logic Levels**

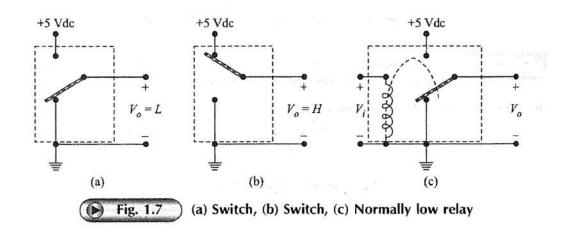

- The digital voltage levels described in Fig. 1.4 can be produced using switches on the next page. The switch is down and  $V_0 = L = 0 = 0$  V de. When the switch is up, as  $V_0 = H = 1 = +5$  V de.

- A switch is easy to use and easy to understand, but it must be operated by hand.

- A *relay* is a switch that is actuated by applying a voltage *Vi* to a coil. The coil current develops a magnetic field that moves the switch an n from one contact to the other.

- > This is indicated with the dashed line drawn between the coil and the relay arm.

- For this particular relay,  $V_0 = L = 0$  Vdc when  $v_i = 0$  V de. Applying a voltage  $v_i$  will actuate the relay, and then  $V_0 = H = +5$  V de. This relay could of course be connected so that its output is low when actuated.

- Switches and relays were useful in the construction of early machines used for calculation and/or logic operations.

- In fact, they are still used to a limited extent in modem computer systems where humans must interact with a system. For instance, on-off power switches, reset, start-stop, and load-unload are functions that might require human initiation.

On the other hand, modem computers are capable of performing billions of switching operations every second! Switches and relays are clearly not capable of this performance, and they have therefore been replaced by transistors (bipolar and/or MOSFET).

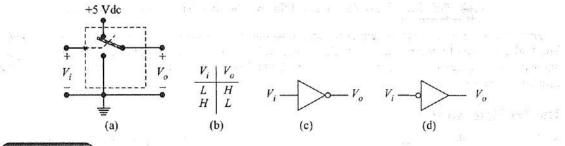

## The Buffer

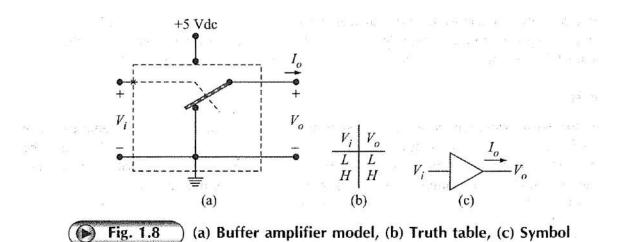

- In order to deliver the necessary load current *1* in digital IC called a *buffer* might be used. A buffer can be thought of as an electronic switch.

- The switch is actuated by the input voltage  $v_i$ . Its operation is similar to the relay. When  $v_i$  is low, the switch is down, and  $V_0$  is low. On the other hand, when  $v_i$  is high, the switch moves up and  $V_0$  is high.

- > Operation of this IC is summarized by using the truth table, or table of combinations. There are only two possible input voltage levels (*L* and *JI*), and the truth table shows the value of  $V_0$  in each case.

Since the buffer is capable of delivering additional current to a load, it is often called a *buffer amplifier*.

The traditional amplifier symbol (a triangle) shown in Fig. 1.8c is used on schematic diagrams. If you're interested in an actual IC buffer, look in the standard TTL logic family. The 5407 or 7407 is a 14-pin IC that contains six buffers.

#### The Tri-State Buffer

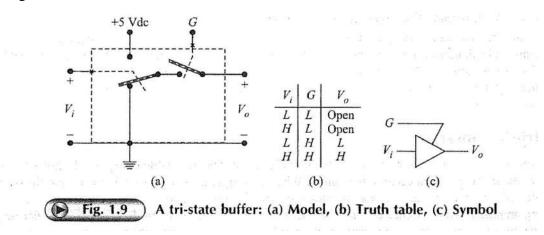

- At the input of a digital system, there may be more than one input signal of interest. Generally speaking, however, it will be necessary to connect only one signal at a time, and thus there is a requirement to connect or disconnect (switch) input signals electronically.

- Similarly, the output of a digital system may need to be directed to more than one destination, one at a time.

- The logic circuit is a simple buffer with an additional switch controlled by an input labeled G. When G is low, this switch is open and the output is "disconnected" from the buffer. When G is high, the switch is closed and the output follows the input.

- That is, the circuit behaves as an ordinary buffer amplifier. In effect, the control signal G connects the buffer to the load or disconnects the buffer from the load.

- When G is high,  $v_0$  is either high or low (two states). However, when G is low, the output is in effect an *open circuit* (a third state).

- Since there are *three* possible states for  $V_0$ , this circuit is called a *tri-state bzttfer*. (*Tri* stands for "three", and thus the term *three-state buffer* is often used.)

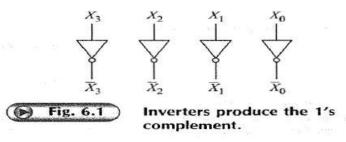

#### **The Inverter**

- One of the most basic operations in a digital system is *inversion*, or *negation*. This requires a circuit that will invert a digital level. This logic circuit is called an *inverter*, or sometimes a *NOT circuit*.

- The switch arrangement in is an inverter. When the input to this circuit is low, the switch remains up and the output is high.

- When the input is high, the switch moves down and the output is low. The truth table for the inverter. Ob Clearly the output is the negative, or the inverse, of the input.

Fig. 1.10 Digital inverter: (a) Model, (b) Truth table, (c) Symbol, (d) Another symbol

- When the inverter is used as a logic circuit, *His* often defined as the "true" state, while *L* is defined as the "false" state. In this sense, the inverter will always provide at its output a signal that is the inverse, or complement, of the signal at its input.

- It is thus called a *negation* or NOT circuit. This makes sense, since there are only two possible states, and therefore *NOT H* must be *L* and NOT *L* must be *H*.

- The inverse complement or of a signal is shown by writing a bar above the symbol. For instance, the complement of A is written as A or A' and this is read as "A bar" A logic expression for the inverter.

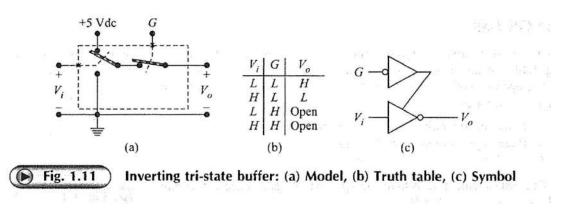

#### The Tri-state Inverter

> A *tri-state inverter* is easy to construct, that when G is low, the inverter to is connected the output. When G is high, the enable switch opens, and the output is disconnected from the inverter.

> The standard logic symbol for this tri-state inverter is given in Fig. 1.11 c. The inverting amplifier symbol indicates that  $V_0$ , is the inverse of v; (the small circle is at the amplifier output).

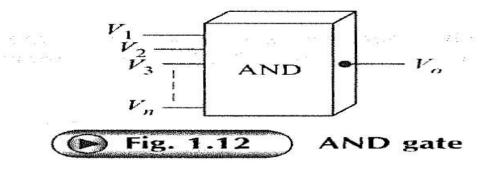

#### The AND Gate

$\triangleright$ An AND gate is a digital circuit having two or more inputs and a single output. The inputs to this gate are labeled  $V_1$ ,  $V_2$ ,  $V_2$ , ... Vn, (there are n inputs), and the output is labeled  $V_0$ .

$\triangleright$ The operation of an AND gate can be expressed in a number of different, but equivalent, ways. For instance.

- If any input is low, V<sub>a</sub> will be low.

V<sub>a</sub> will be high only when all inputs are high.

V<sub>a</sub> = H only if V<sub>1</sub> = H, and V<sub>2</sub> = H, and V<sub>3</sub> = H, ... and V<sub>n</sub> = H.

This last statement leads to the designation AND gate, since  $V_1$ and  $V_2$ , and  $V_3$ , ... and  $V_n$  must all be high in order for  $V_n$  to be high.

- A model for an AND gate having 2 inputs. This gate can be used to make "logical"  $\geq$ decisions; for example, "If  $V_1$  and  $V_2$ , then  $V_{0,.}$ " As a result, it is referred to as a digital logic circuit, as are all AND gates.

- From the model, it is seen that  $V_1 = H$  closes the upper switch, and  $V_2 = H$  closes the  $\geq$ lower switch. Clearly,  $V_0 = H$  only when both  $V_1$  and  $V_2$  are high. This can be expressed in the form of a logic equation written as

$$V_o = V_1 \text{ AND } V_2$$

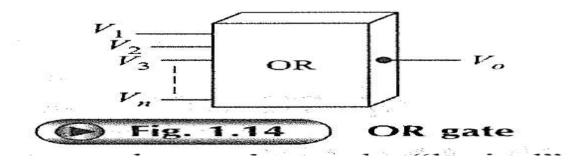

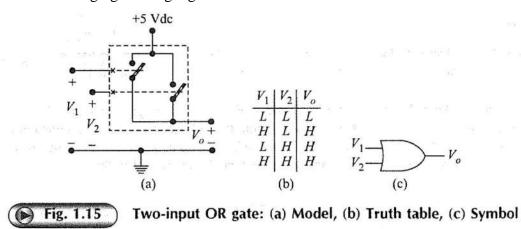

## The OR Gate

> An OR gate is also a digital circuit having 2 or more inputs and a single output as indicated in

- 1.  $V_{o}$  will be low only when all inputs are low.

2. If any input is high, V will be high. 3.  $V_o = H$  if  $V_1$ , or  $V_2$  or  $V_3$ , ... or  $V_n = H$ .

This last statement leads to the designation OR gate, since  $V_o = H$  only if  $V_1$  or  $V_2$ , or  $V_3$ , ...  $V_n = H$ .

- ▶ A model for an OR gate having 2 inputs is shown in Fig. 1.15a. This gate can be used to make "logical" decisions; for example, "If  $V_1$  or  $V_2$ , then  $V_0$ ." As a result, it is referred to as a digital logic circuit, as are all OR gates.

- From the model, it is seen that  $V_1 = H$  closes the upper switch, and  $V_2 = H$  closes the lower switch. Clearly, V = H if either  $V_1$  or  $V_2$  is high. This can be expressed in the form of a "logic" equation written as

The operation is summarized in the truth table in Fig. 1.15b. The symbol for a 2-input OR gate is shown in Fig. 1.15c. Thus, OR is a logic operation which is realized here through gate a logic gate.

$V_o = V_1 \text{ OR } V_2$

#### MOVING AND STORING DIGITAL INFORMATION

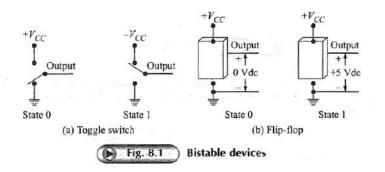

#### **Memory Elements**

- A digital memory element is a device or perhaps a circuit that will maintain a desired logic level at its output till it is changed by changing the input condition.

- The switch is placed such that its output is low, and it will remain low without any further action.

- > Thus, it will "remember" that  $V_0 = L$ . Since L = 0 = 0 Vdc, the switch can be thought of as "holding" or "storing" a logic 0. In Fig. I. 7b,  $V_0 = H$ , and it will remain high without any further action. The switch remembers that  $V_0 = H$ .

- > In this case, the switch is holding or storing a logic 1, since H = I = +5 V de. It is easy to see that this switch can be used to store a digital level, and it will remember the stored level indefinitely.

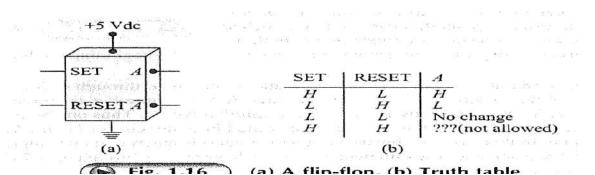

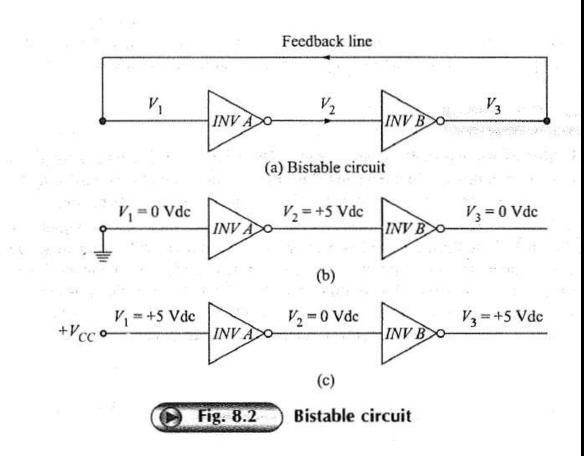

- The simplest electronic circuit used as a memory element is called a *flip:flop*. Since a flip-flop is constructed using transistors, its operation depends upon de supply voltage(s).

- The flip-flop can be used to store a logic level (high or low), and it will retain a stored level indefinitely provided the de supply voltage is maintained. An interruption in the de supply voltage will result in loss of the stored logic level.

- When power is first applied to a flip-flop (turning the system on first thing in the morning), it will store either a high or a low. This is a "random" result, and it must be accounted for in any digital system. Generally, a signal such as MASTER RESET or power-on reset will be used to *initialize* all storage elements.

- The two inputs are SET and RESET, and the output is A. The output labeled A is simply the *inverse* of A. Here's how it works:

- 1. When SET= Hand RESET = L, the flip-flop is *set*, and A = H.

- 2. When SET = L and RESET = H, the flip-flop is reset, and A = L.

- 3. Holding SET= Land RESET= L disables the flip-flop and its output remains unchanged.

- 4. Applying SET= Hand RESET= Hat the same time is not allowed, since this is a request to *set* and *reset* at the same time-an impossible request!

- To summarize, the flip-flop is SET, it stores a high (a logic 1). When it is RESET, it stores a low (a logic 0).

- A simple flip-flop such as this is often called a *latch*, since its operation is similar to a switch. A 7475 is an IC in the TTL family that contains four similar flip-flops.

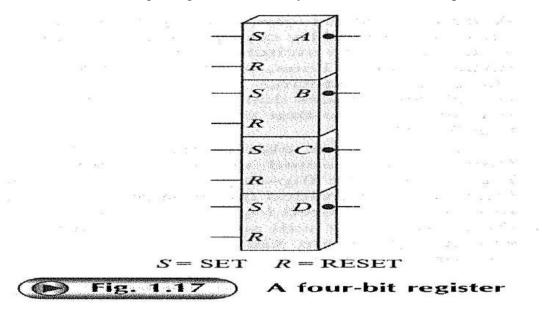

## Registers

A group of flip-flops can be connected together to store more than a single logic level. For instance, the four flip-flops can be used to store four logic levels.

- As such, they could be used to store any of the ten binary numbers given in Table. As an example, if A is SET, B is RESET, C is SET, and D is RESET, this will store the binary number DCBA = LHLH = 0101, which is equivalent to decimal 5.

- When we speak of decimal numbers, in each position a number is called a *decimal digit*, or simply a digit. For example, the decimal number 847 has three digits.

- When we speak of binary numbers, each position in the number is called a *binary digit*, or *bit*. (The term "binary digit!" has been shortened to "bit.")

- For example, the binary number 0101 is composed of four bits; It is a 4-bit binary number. The four flip-flops can be used to store any 4-bit binary number.

- A group of flip-flops used to store a binary number is called a *register*, or sometimes a *storage register*. The register is a 4-bit register.

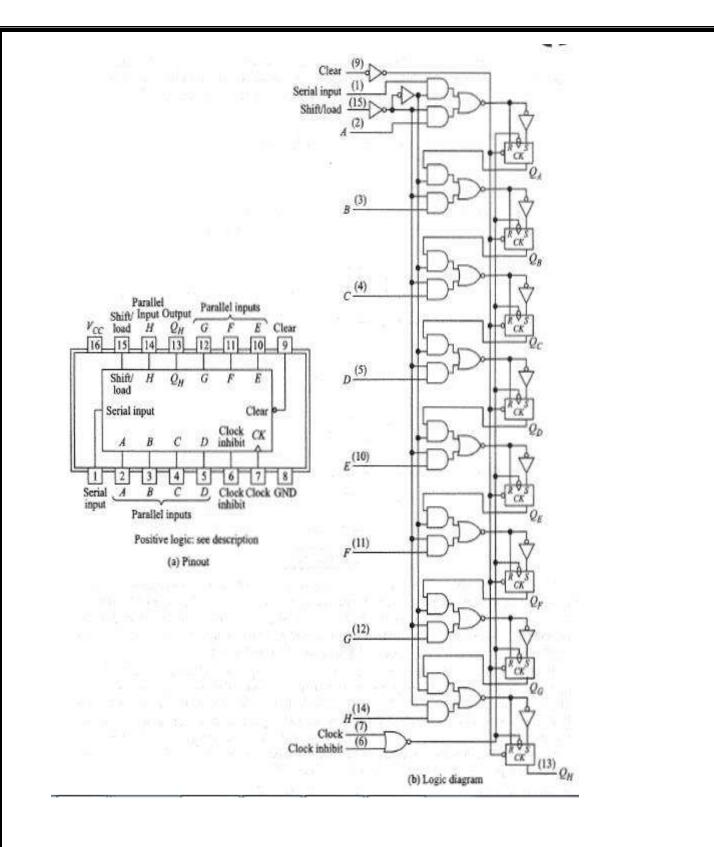

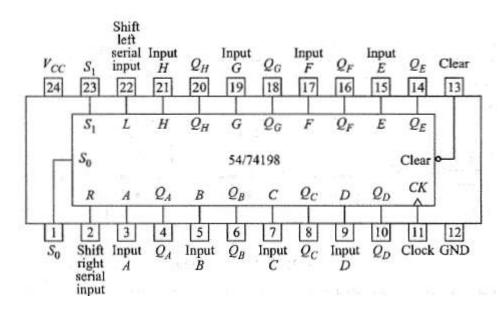

- There are eight flip-flops in an 8-bit register, and so on. In the TTL family, the 7 4198 is an 8-bit register. Clearly a register can be used to store decimal numbers in their binary equivalent form.

- In general, binary numbers such as this are referred to as *data*. A register is a fundamental building block in a microprocessor or digital computer, and you can now see the beginnings of how these systems are used for computation.

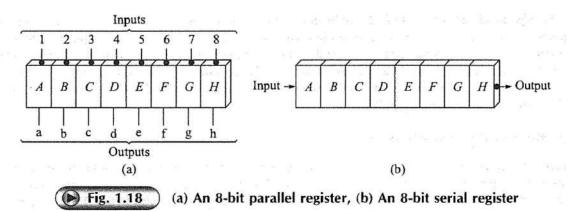

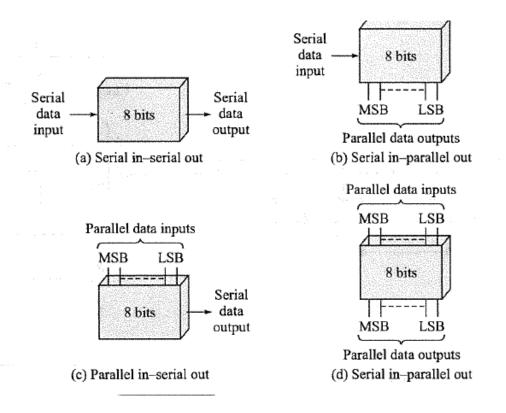

The register in Fig. 1.18a has 8 inputs, 1 through 8, and 8 outputs, a through h. It is constructed using eight flip-flops and some additional electronic circuits.

- A binary number is stored in this register by applying the appropriate level (high or low) at each input *simultaneously*. Thus one bit is "shifted" into each flip-flop in the register.

- The binary number is said to be shifted into the register *in parallel*, since all bits are entered at the same time. In this case, binary the number (or data) is entered in one single operation.

- Once a number is stored in this register, it appears immediately at the 8 outputs, a through h. A 74198 is an example of an 8-bit *parallel register*.

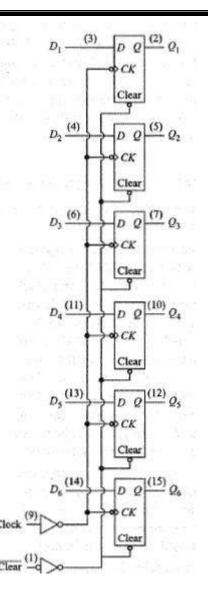

- The register in Fig. 1.18b has a single input and a single output. It is also constructed using eight flip-flops and some additional electronic circuits.

- It will store an 8-bit binary number, but the number must be entered into the register one bit at a time at the input. It thus requires eight operations to store an 8-bit number. This is how it is done.

- The first bit of the binary number is entered in flip-flop A at the input. The second

$\geq$

bit is

then entered into flip-flop *A*, and at the same time the first bit in flip-flop *A* is passed along (shifted) to flip-flop *B*.

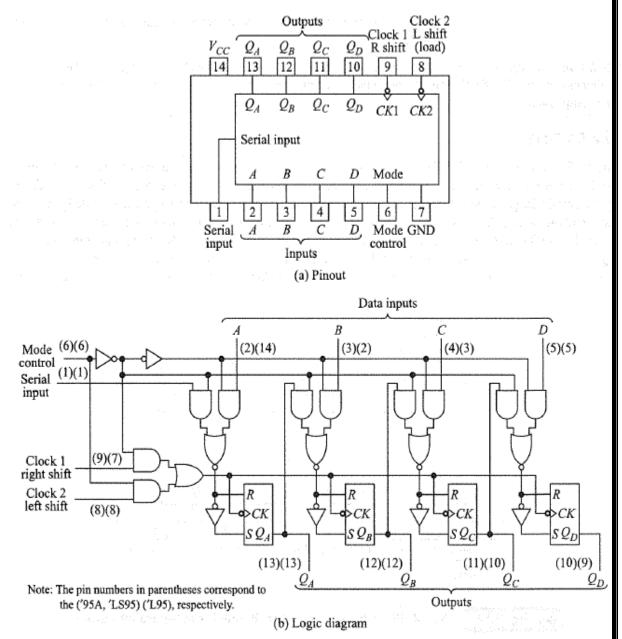

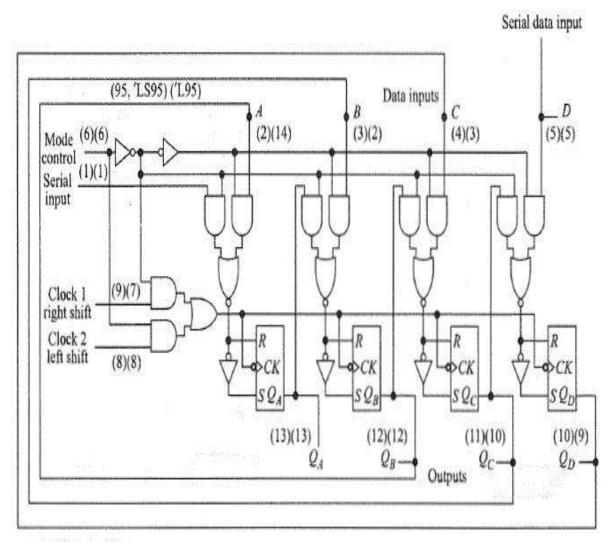

When the third bit enters A, the bit in A goes to B and the bit in B goes to C. This shift right process is repeated, and after eight operations, the 8-bit number will be stored in the register. Since the bits are entered one after the other in a serial fashion, this is called a *serial register*.

For a stored number to be extracted from this register, the bits must he shifted through the flip-flops from left to right. The stored number will then appear at the output, one bit at a time. It requires eight operations, or eight right shifts, to extract the stored number.

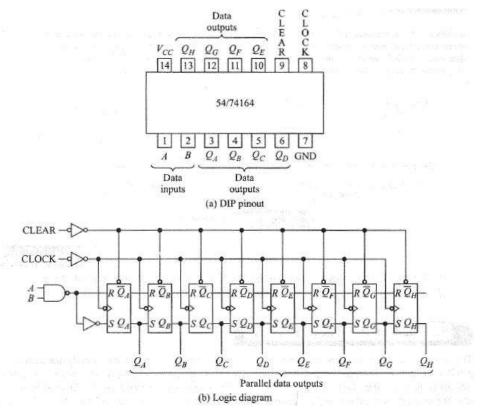

A 74164 TTL is an example of an 8-bit serial register (this particular IC also provides parallel outputs).

#### **Transferring Digital Data**

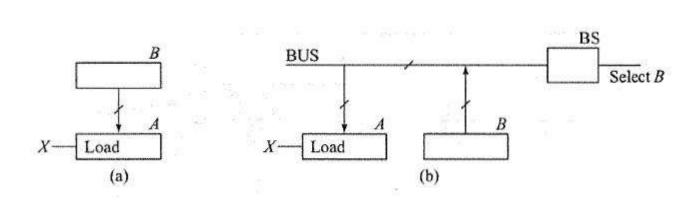

- A register is used to enter data (binary numbers) into a microprocessor or computer. A register is also used to extract data from a computer and direct it to an external destination are Wire cables generally the means for connecting systems.

- If a parallel register is used, the data is said to be shifted in parallel. The connector in this case must have one pin for each bit, and the cable must have at least one wire for each bit.

- An 8-bit register requires a cable having at least 8 wires, a 16-bit register must have at least 16 wires, and so on.

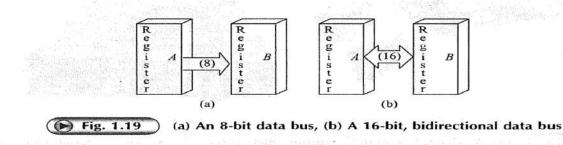

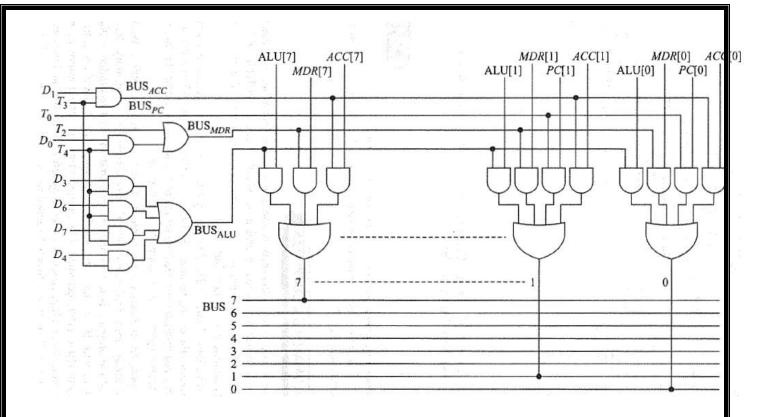

- Data are also transferred (shifted) between registers within a digital system. Instead of drawing all 8 (or16 or 32) wires on a schematic, it is common practice to use an arrow between the registers.

- The number 8 in parentheses means that there are eight wires. In this case, there are eight connections used to transfer 8 bits of data in parallel from register A to register B. The eight wires represented by this arrow are called a *data bus*.

➤ The double arrow shown in Fig. 1.19b means 16 bits of data can be shifted in parallel from A to B or from B to A. This is a 16-bit *bidirectional data bus*.

- On the other hand, data can be shifted serially into or out of a serial register, and only one wire ( connection) is required for the data.

- Clearly, parallel operation will transfer data into or out of a computer system much more rapidly than serial operation.

- The price paid for this gain in speed is an increase complexity, in in terms of both the electronic circuits and the increased number of connections (wires in the cable).

- The computer connector where data is entered or extracted is frequently called a *port*. Nearly all computer systems have available both a serial port and a parallel port.

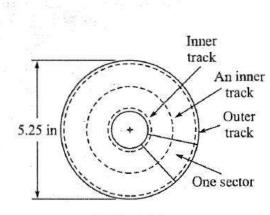

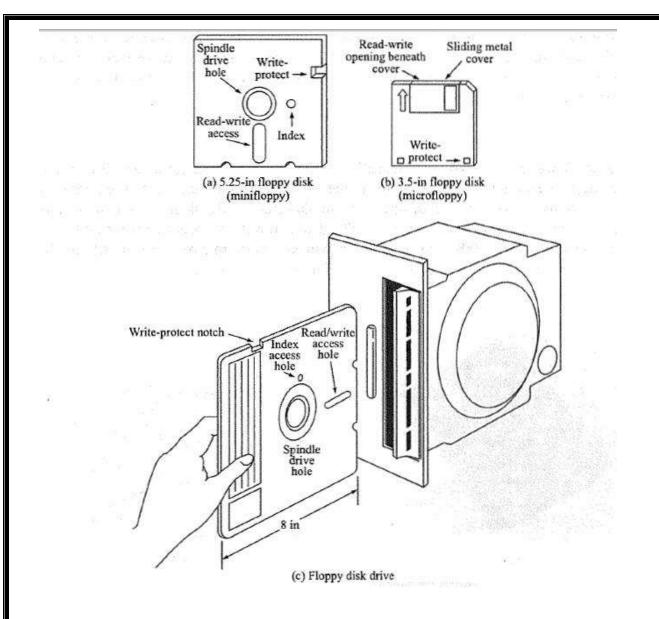

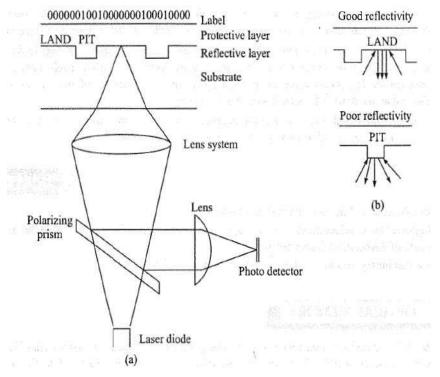

### **Magnetic and Optical Memory**

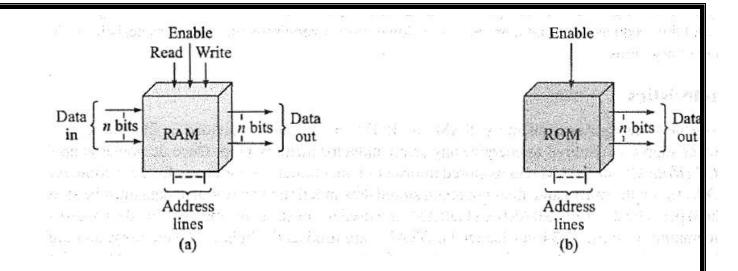

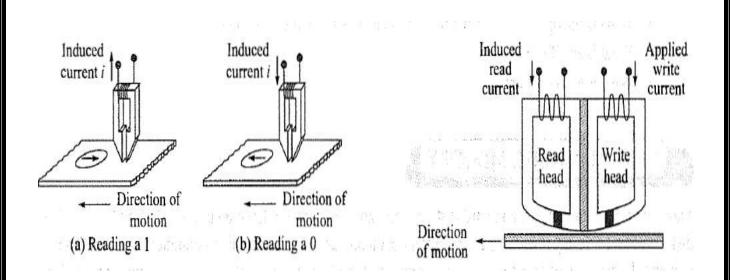

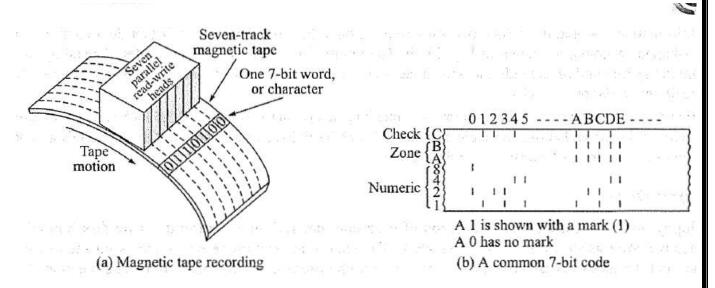

- Any memory element must be capable of storing or retaining only two logic levels, and there are numerous devices with the appropriate electronic circuits used for this purpose.

- One of the most common systems for memory makes use of the fact that a magnetic material can be magnetized with two different orientations.

- Thus, magnetizing spots on a strip of magnetic tape, or on a hard disk with a magnetic coating, or on a magnetic floppy disk are well known used and widely memory systems.

## **DIGITAL OPERATIONS**

#### Counters

- It was mentioned previously that counting is an operation easily performed by a digital circuit.

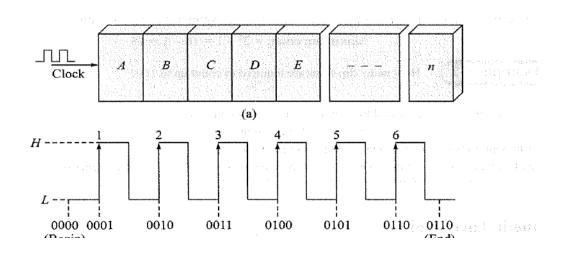

- A digital circuit designed to keep track of a number of events, or to count, is called a *counter:* The counter is constructed using a number of flip-flops (n) and additional electronic circuits.

- It is similar to a storage register, since it is capable of storing a binary number. The input to this counter is the rectangular waveform labeled *clock*. Each time the clock signal changes state from low to high, the counter will add one (1) to the number stored in its flip-flops.

- In other words, this counter will count the number of clock transitions from low to high. A clock having a small circle (bubble) in the input side would count clock transitions from high to low. This is the concept of *active* is, an action occurs when the input is low.

- A four-flip-flop counter can count decimal numbers from 0 to 15. To count higher, it is necessary to add more flip-flops. It is easy to determine the maximum decimal count in terms of the number of flip-flops using the following relation

$$Maximum count = 2'' - 1$$

(1.1)

where n = number of flip-flops.

The term 2" means 2 raised to the nth power, that is, 2 multiplied by itself n times.

For example,

$$2^2 = 2 x^2 = 4$$

$2^3 = 2 X 2 X 2 = 8$

$2^4 = 2 X 2 X 2 X 2 '''-' 16$

$$2^{3} = 2 \times 2 \times 2 \times 2 \times 2 \times 2 = 32$$

$2^{6} = 2 \times 2 \times 2 \times 2 \times 2 \times 2 \times 2 = 64$

$2^{7} = 128$

$2^{8} = 256$

$2^{9} = 512$

$2^{10} = 1024$

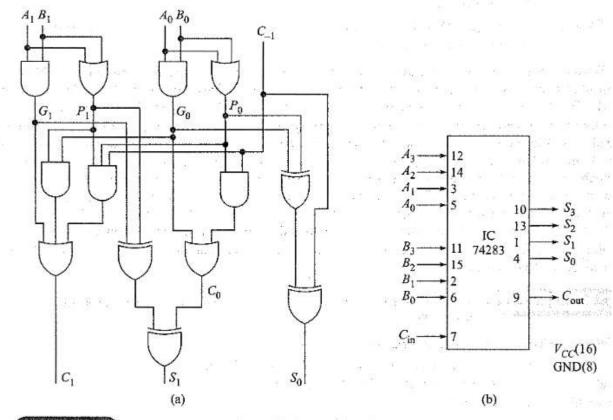

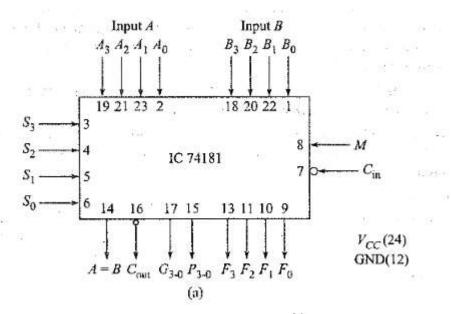

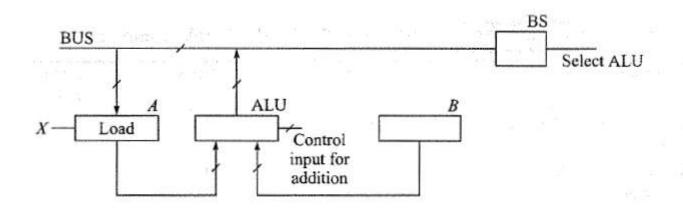

## **Arithmetic logic Unit**

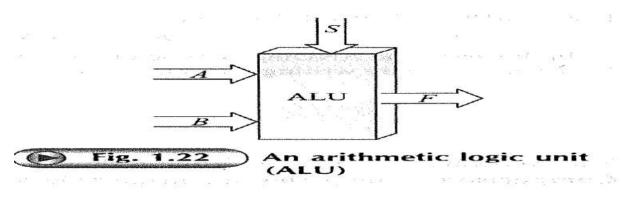

- An arithmetic logic unit (ALU) is a digital circuit capable ofperforming both arithmetic and logic operations.

- The basic arithmetic operations performed by an ALU are addition (+) and subtraction(-:). Multiplication (\*) and division (/) of digital numbers are accomplished with other digital circuits.

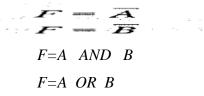

- Logic operations will usually include inversion (NOT), AND, and OR. The ALU represented has two data inputs; the

## **Addition and Subtraction:**

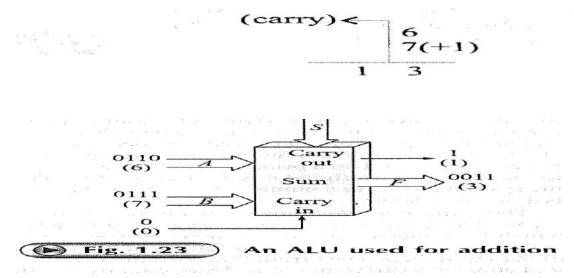

If the proper digital levels are applied to the inputs of the S bus, the ALU can be used to add two digital numbers.

- The two numbers to be added are represented by the proper logic levels at A and B, and the SUM of these two numbers will appear at output F.

- > In event the sum of the two numbers generates a carry, an *H* will appear at the CARRY OUT. To illustrate, suppose we wish to perform the addition 6 + 7 = 13. Here's how we might do it with decimal numbers.

- The digital levels illustrated result in the addition of these two numbers. The equivalent numbers decimal are shown in parentheses. Notice that the CARRY IN allows this ALU to add two numbers, plus a carry.

- ➢ By changing the control levels at the S bus, this ALU will determine the difference A -B (subtraction).

- ➢ In this case, the digital levels at the *F* bus represent the DIFFERENCE, rather than the SUM.

#### **Logic Functions**

- By changing the digital levels at the S bus, the ALU can be used to perform a number of different logic functions relative to the two digital inputs.

- > The desired function appears at the *F* bus. Here are some of the possibilities:

> The operations are carried out "bit by bit." For example,

If A = 1010 then  $F = \bar{A} = 0101$

If A = 1010 and if B = 0110, then

$$F = A \text{ AND } B = 1010 \text{ AND } 0110 = 0010$$

- In this case, the AND ing is done on the corresponding bit of each input. There are tour AND operations.

- ➢ It's easier to see by writing the data as follows:

A = 1010|||| B = 0110F = 0010

The "vertical lines" between A and B show which bits are AND.

# Comparison

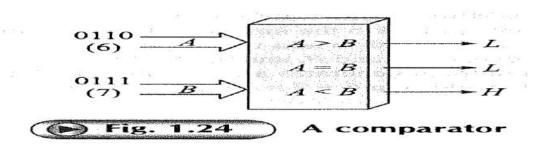

- Comparing the magnitude of two numbers is an important logical operation. The circuit is a *comparator*. It is capable of comparing two digital numbers and indicating whether the magnitude of one is greater than, less than, or equal to the other.

- For example, if A = 0110 (decimal 6) and B = 0111 (decimal 7), then the output A < B will be high.

- The other two outputs will be low. A 7485 in the TTL family is a 4-bit comparator similar. Also, the 74181 ALU can be used with the same results.

#### Input/Output

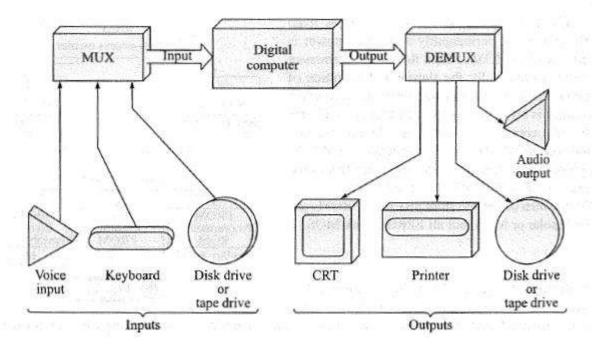

- In order for any digital system to be useful, there must be some provision for entering data into the system and also some method of extracting data from the system.

- In the case of a computer, information is frequently entered by typing on a keyboard or perhaps by using a magnetic floppy disk. Useful information can be obtained from the computer by examining the visual displays on a cathode-ray tube (CRT) or by reading material produced on a printer.

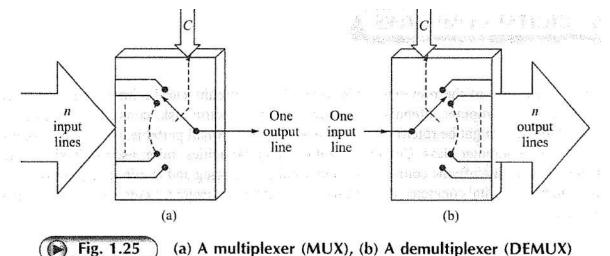

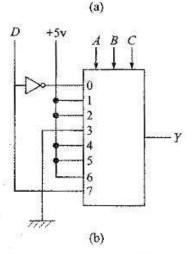

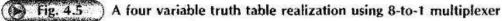

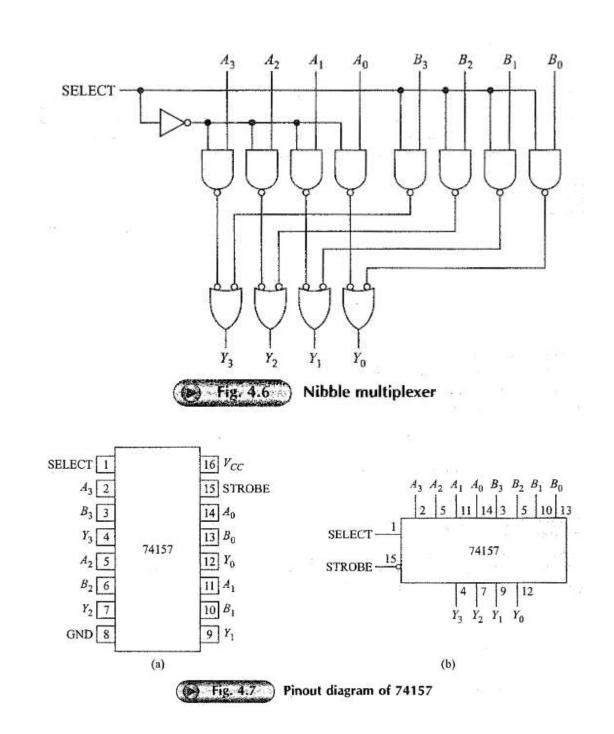

- Clearly there is a requirement to connect multiple input devices, one at a time, to the system. The digital circuit used for this operation is a multiplexer.

- Likewise, there is a need to connect the system output to a number of different destinations, one at a time. The digital circuit used for this purpose is a demultiplexer.

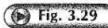

- The term *multiplex* means "many into one." A *multiplexer (MUX)* can be represented. There are *n* input lines. Each line is used to shift digital data serially.

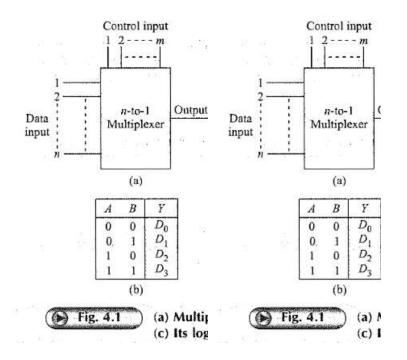

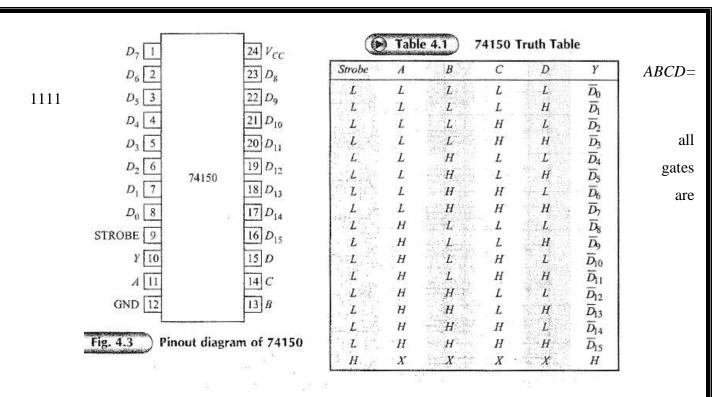

- Thus, data from multiple sources can be connected to a single input port, one at a time. An example of a MUX is the 74150 in the TTL family. It has 16 input lines and a single output line.

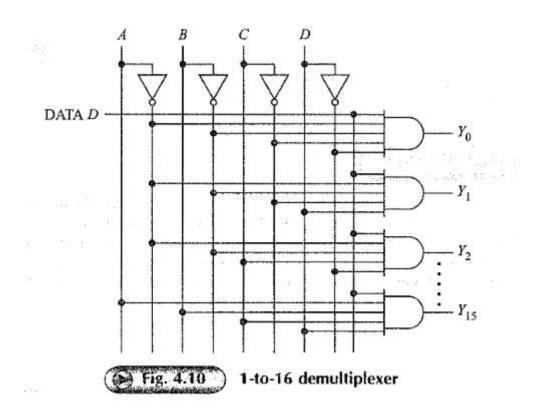

- > The opposite of multiplex is *demultiplex*, "onewhich means into many." A *demultiplexer (DEMUX)* can be represented. This digital circuit simply connects the single data input line to one of the n output lines, one at a time, according to the levels on the C bus.

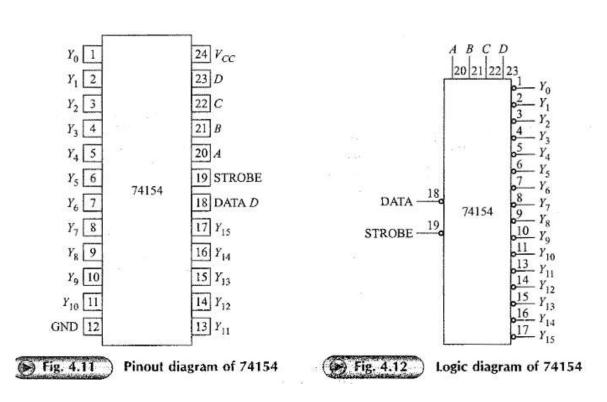

- Thus serial data from the computer output port can be directed to different destinations, one at a time. An example of a DEMUX is the TTL 74154, which can be used to connect a single input to any one of 16 outputs, one at a time.

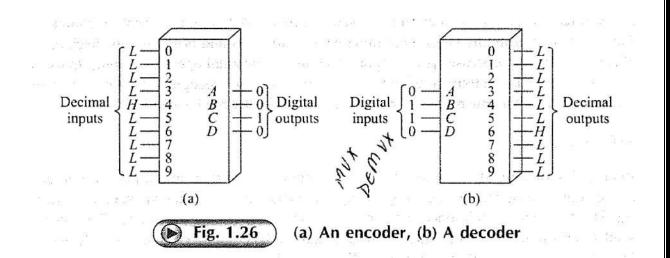

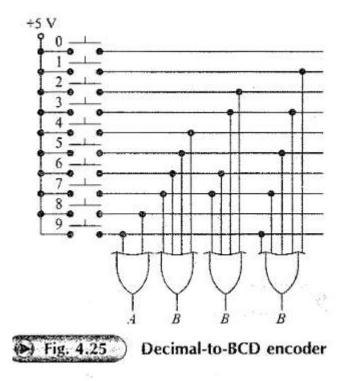

- Any information entered into a digital system must be in the form of a digital number. A circuit that changes data into the required digital form is called an *encoder*.

- The encoder on the next page will change a decimal number into its binary equivalent. It may be used with a keyboard.

- For instance, depressing the number 4 key on a keyboard will cause input line 4 to this encoder to be high (the other inputs are all low). The result will be decimal 4, binary 0100, at the encoder output as shown.

- Taking digital information from the output of a computer and changing it into another form is accomplished with a *decoder*, for example, changing the digital number O110 ( decimal 6) into its decimal form.

#### **DIGITAL COMPUTERS**

#### Terms

- > Digital circuits can be interconnected to construct a digital computer.

- A computer intended to perform a very specific task, constructed with a minimum number of components, might be referred to as a *microcomputer*.

- Small portable, or desktop, computers are usually in the microcomputer class. Computers with greater capacities, often used in business, are called *minicomputers*.

- A large mainframe computer system capable of storing and manipulating massive quantities of data, for example, a digital computer system used by a bank or an insurance company, might then be called *maxi computer*.

#### Uses

The inclusion of an ALU with additional logic circuits provides arithmetic capabilities (addition, subtraction, multiplication, division).

The logic portion of the ALU means the computer can be used to make logical decisions. Beyond these basic functions, a digital computer can be used to process data (balance bank accounts), to rapidly perform otherwise time-consuming tasks ( determine payroll amounts and print out paychecks), to precisely monitor and control intricate processes (life support systems in a hospital operating room).

#### **Basic Configurations**

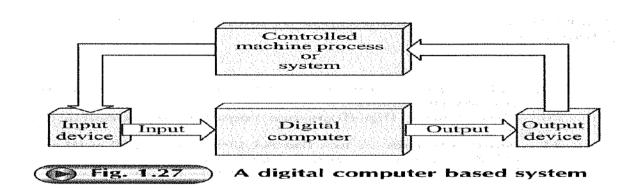

- A microcomputer designed to control a given machine, process, or system might be represented in fig. The control produced signals by the computer appear as the output bus and are sent to an output device.

- Here, the signals are properly conditioned and sent to the mechanism being controlled. The controlled entity must then send signals indicating its present condition back to the computer via an input device and via the input bus.

- The computer analyzes these present condition signals, determines any necessary action, and sends required correction signals to out the system.

A microcomputer system might be designed to irrigate the lawn area of a park. Watering is to be done only at night, when the soil moisture falls below a given value.

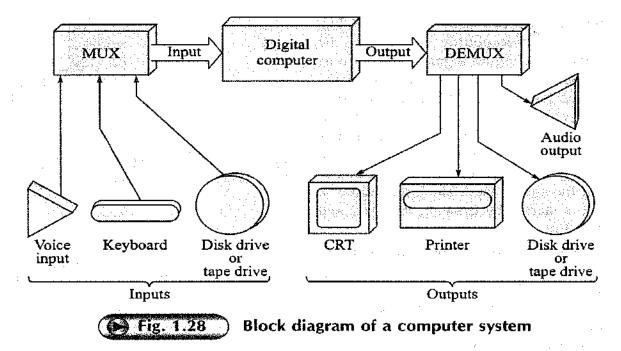

> This allows the connection of a number of different input devices:

A keyboard for typewritten entry of alphanumeric informationA disk drive or tape drive for entering data stored in magnetic form A microphone for voice input

> The DEMUX on the output bus allows numerous possibilities for receiving information from the computer: Familiar The CRT for a visual display.A printer to provide printed material (called *hard copy*).

- A disk or tape drive to record data in magnetic form Perhaps a speaker for audio information

- A minicomputer such as this can be used for many different tasks. It can be used as a word processor, for data processing, for communication via telephone (both voice and fax), for training in an educational setting, for computer games, and so on!

- For instance, a maxi computer will likely have more than one printer, and perhaps even different types of printers.

- It will generally have a large number of users, all of whom desire access to the system at the same time.

- > One workstation must then be provided for each user.

- A keyboard and a CRT are the minimum components required at each workstation. The digital circuits used to construct maxi computer systems are necessarily more complicated than minicomputer systems, and they may operate at a much faster rate.

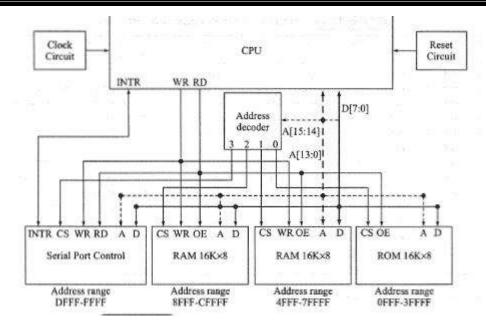

# **Basic Computer Architecture**

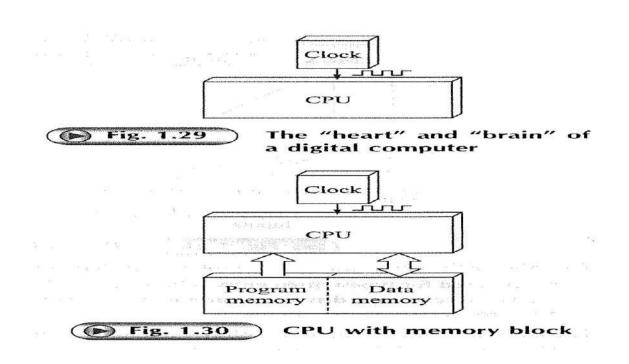

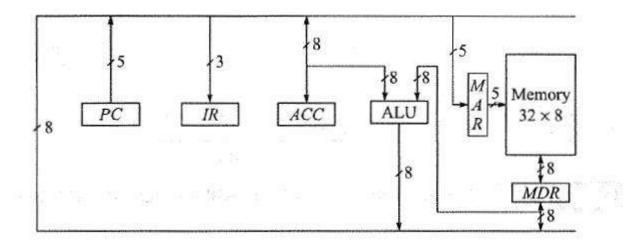

- The central processing unit (CPU) is the brain of a digital computer. It is constructed using an ALU along with a number of registers and counters.

- The CPU is therefore the primary center for computation and decision making. All the operations within the CPU, and indeed within the computer itself, must be carefully coordinated.

- A digital signal refered to as the system clock is used as a reference to time when specific operations take place. The clock signal is usually a periodic, rectangular waveform.

- Using a crystal in the clock circuit allows the accuracy and stability of the clock frequency, to be controlled with great precision.

- The clock provides a "heartbeat" for the computer. A block diagram of a digital computer is started by drawing the CPU and clock.

The CPU is capable of computation and decision, but it must have specific instructions telling it exactly *what* to do and *when* to do it. This set of instructions is called a *program*.

- A program is a detailed list of operations written by a human programmer. The programmer decides what the computer is to do and when it should be done, and then writes a list of instructions to be carried out in the proper order.

- The program is entered into the computer, using perhaps a keyboard, and stored in the computer *memory*.

- The CPU can then "fetch" from memory one instruction at a time, in the given order. It will execute the instruction and then fetch the next instruction. With this repeated fetch and-execute cycle, the CPU will accomplish the desired task. A memory block used for program storage has been added.

- A portion of the memory block is labeled *data*. This is the area where the information being processed by the computer is stored. In addition, this is where the CPU stores the results of computations and/or decisions made.

- Since the CPU takes ("reads") data from memory, as well as returns ("writes") data into memory, the memory data bus is bidirectional. By contrast, the program data

bus is not bidirectional, since information on this bus is always from memory to CPU.

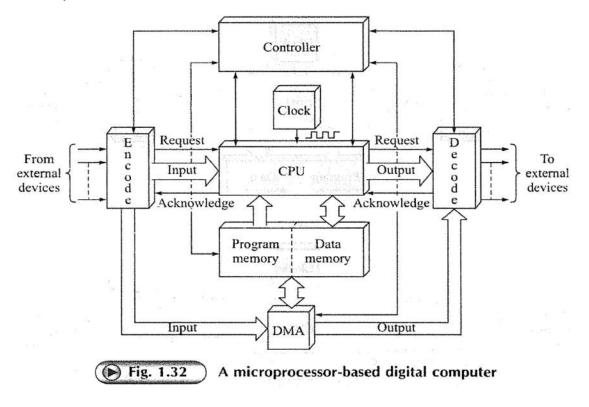

- The CPU communicates with the "outside world" by means of the input encoders and the output decoders.

- The ability to multiplex inputs and de multiplex outputs may also be included in the input/output blocks that have been added. This configuration is sometimes quite inefficient, since all information entering or exiting the computer must pass through the CPU.

- The CPU operates at a much faster rate than most external devices, and it must *wait* while data are being entered or exited: A *direct memory access (DMA)* block is generally included to alleviate this problem.

- The DMA allows information to move directly from an input device into memory or from memory directly to an output device.

- While information is being transferred via the DMA, the CPU is free to carry on its computational or logical operations. This greatly improves system efficiency as well as speed of operation.

- Before data can be entered into the computer, a signal on the input request line asks the computer for "permission" to input information.

- For instance, depressing the enter key on a keyboard will generate an input request signal. When the CPU is ready, a signal is generated on the acknowledge line, and data will be entered via the DMA into the memory. This request-acknowledge sequence is often called *handshaking*.

- A similar handshaking must occur when the CPU is ready to deliver data to an external device. However, in this case, the CPU makes an output request, and the external device gives permission.

- All of these blocks are operated in synchronism with the clock, but additional direction must be provided.

- The *controller* is the unit that decides which block "goes first" (establishes priorities), decides the order in which external devices are serviced, routes data along the various buses such that no conflicts occur, and controls the overall operation of the system.

A microprocessor is often used as the basic IC around which a micro computer or minicomputer is constructed. Numerous computers have been designed, beginning with the 8080 microprocessor. Improvements to this basic IC have led to the development of a family of microprocessor units including the 8085 and the 8086.

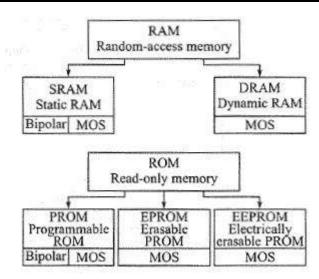

## DIGITAL INTEGRATED CIRCUITS

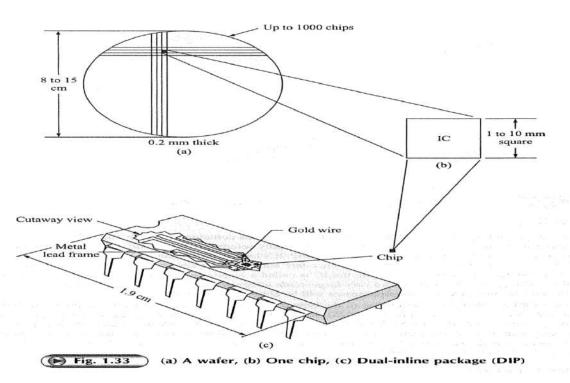

- A digital IC is constructed by an interconnection of resistors, transistors, and perhaps capacitors, small all of which have been formed on the surface of a semiconductor wafer. The entire circuit resides on a tiny piece of semiconductor material called a *chip*.

- The semiconductor wafer is typically a slice of mono crystal line about silicon 0.2 mm thick and perhaps 8 to 15 cm in diameter. The wafer is divided checkerboard fashion into 1000 or so rectangular areas.

Each area will become a single chip. The resistors and transistors necessary for each digital circuit are then formed on each chip by a series of semiconductor processing

steps. In this fashion, identical digital circuits are manufactured simultaneously on the same silicon wafer.-

- After the processing steps are completed, the wafer is separated into individual chips. Each chip is a digital circuit, for example, an inverter or an AND gate.

- An individual digital circuit may have only a few components, but some circuits have a few hundred components!

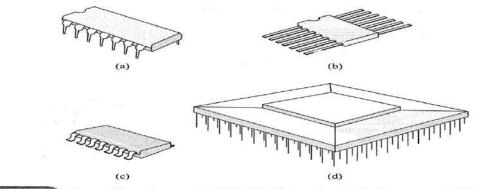

- Each chip is then mounted in a suitable package, as shown in Fig. 1.33c. The package illustrated here is a 14-pin *dual-inline package (DIP)*.

# **IC Families**

- ICs are categorized by size according to the number of gates contained on each chip. There is no absolute rule, but an IC having fewer than 10 or 12 gates is usually referred to as a *small-scale integration (SSI) IC*.

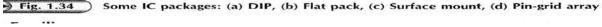

- For instance, a 7404 has six inverters in a 14-pin DIP. ICs having more than 12 but fewer than 100 gates are called *medium-scale integration (MS!) !Cs;* encoders and decoders are examples of MSI ICs.

- If there are more than 100 gates but fewer than 1000, the IC is called a *large-scale integration (LSI) JC*. An IC having more greater than 1000 is referred to as a ve,y *large-scale integration (VLSI) JC*.

- A large complex system such as semiconductor memory or a microprocessor will be either LSI or VLSI.

- ICs are further categorized according to the type of transistors used. The two basic transistor types are *bipolar* and *metal-oxide-semiconductor* (MOS).

- Bipolar technology is faster but requires more power, and is generally preferred for SSI and MSI. MOS is slower, but requires much less power occupies and also a much smaller chip area for a given function.

- MOS is therefore preferred for LSI and is widely used in applications such as pocket calculators, wristwatches, hearing aids, and so on. For the moment, let's consider the overall characteristics of each digital IC family.

## **Bipolar Transistors**

There are two important digital circuit families constructed bipolar using transistors:

- Transistor-Transistor Logic (TTL)

- Emitter-Coupled Logic (ECL)

#### **Transistor-Transistor Logic**

- TTL was first introduced by Texas Instruments in 1964 using the numbers 54XX and 74XX. These two families are now widely available from a number of different manufacturers.

- The 74XX ICs operate over a temperature range of 0°C to 75°C. The 54XX devices are more rugged; they operate over a temperature range of -55°C to+ I25°C. As you might expect, the 54XX devices are more expensive.

|             |      | Table 1.2 | Some Standard | Some Standard Digital Circuits |    |

|-------------|------|-----------|---------------|--------------------------------|----|

| e egy a des | TTL  | ECL       | CMOS          | Function                       |    |

|             | 7400 |           | 74HC00        | Quad 2-input NAND gate         | 35 |

|             | 7402 | MC10102   | 74HC02        | Quad 2-input NOR gate          |    |

|             | 7404 |           | 74HC04        | Hex inverter                   |    |

| ARY WATE    | 7408 | MC10104   | 74HC08        | Quad 2-input AND gate          |    |

|             | 7432 | MC10103   | 74HC32        | Quad 2-input OR gate           |    |

- Otherwise, the logical operations of these two families are the same. In each case, the XX portion of the part number refers to a specific device.

- For instance, "04" stands for inverter, and a 7404 is a TTL inverter. A 7411 is a TTL AND gate, and so on. When there is no danger of confusion, it is common practice to shorten the description by omitting the first two digits.

- ➢ In the interest of higher operating speed, the 74XX family was improved with the introduction of the 74HXX (where the H stands for high speed) family of devices.

- The price paid for increased speed was an increase in power required to operate each gate. This led to another family of devices designed to minimize power requirements-the 74LXX (where the L stands for low power) series.

- A major improvement in the TTL series came with the development of a special transistor arrangement called a *Schottky transistor*.

- Using this device, the 74SXX (S for Schottky) family came into being. These devices greatly improved operating speed, but again at the cost of increased power consumption. At this point, a family of devices designated 74LSXX (low-power Schottky) was developed.

- The 74LSXX family offers high-speed operation with minimal power consumption and today is preferred in most designs. The original 7400 also remains popular.

- There are two additional families, 74ASXX (advanced Schottky) and 74ALSXX (advanced low-power Schottky), available.

### **Emitter-Coupled Logic**

- Emitter-coupled logic (ECL) is considerably faster than any of the TTL families, but the power required for each gate is also much higher.

- With a propagation delay of only 2 ns, the industry standard for ECL circuits is 10,000 ECL, abbreviated 10K. The 100K (100,000) series is even faster, with a delay time of only 1 ns. Motorola markets a family of devices designated MECL 10K and MECL 10KH (Motorola Emitter coupled Logic).

#### **MOS Transistors**

- Three digital logic families constructed using MOS field-effect transistors (MOSFETs):

- **PMOS** Using p-channel MOSFETs

- NMOS Using n-channel MOSFETs

- **CMOS** Using both n-channel and p-channel MOSFETs

|        | Table 1.3          | TTL Power-Delay Values  |                |  |

|--------|--------------------|-------------------------|----------------|--|

| Type   | Name               | Power, mW               | Delay Time, ns |  |

| 74XX   | Standard TTL       | VERN OFFICE STREET      | 10             |  |

| 74HXX  | High-speed TTL     | 1500 ( 1.22 ) ( Settis) | 6              |  |

| 74LXX  | Low-power TTL      | 网络索马德国和东西中方公司           | 35             |  |

| 74SXX  | Schottky TTL       | 20                      | 3              |  |

| 74LSXX | Low-power Schottky | 2                       | 10             |  |

- > PMOS, the slowest and oldest type, is nearly obsolete today.

- NMOS dominates the LSI field and is widely used in semiconductor memories micro processors.

- CMOS is preferred where individual logic circuits are used and where very low power consumption is required.

# **Digital logic Symbols**

- ➤ The Institute of Electrical and Electronics Engineers (IEEE) along with the American National Standards Institute (ANSI) have developed a new symbolic language and set of symbols to be used with digital logic circuits.

- These new symbols are now being used on manufacturers' data sheets along with traditional symbols. The most recent revision of *IEEE Standard Graphic Symbols for Logic Functions*, ANSI/IEEE Std 91-1984, provides for two different types of symbols.

- Symbols of the first type, called *distinctive-shape symbols*, are exactly as have been shown throughout this chapter.

- The second system, which is called the *rectangular-shape system*, uses a rectangular box with a special symbol for each type of gate. The IEEE standard does not express a preference for either shape.

- A rectangular box is used for the gate, the input is labeled A, and the output is labeled Y.

- The triangle on the output line signifies that the output is active when low. Thus, when the input is active (high), the output will be active (low).

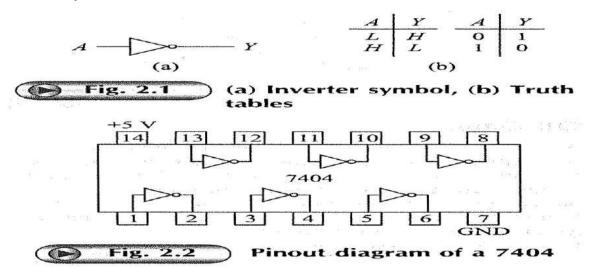

The 7404 is a hex inverter; that is, it is an IC that contains six inverters. The DIP package for this device is shown in Fig. 1.36a, along with the proper pin numbers on the package. Figure 1.36b shows the six standard logic symbols for the inverters.

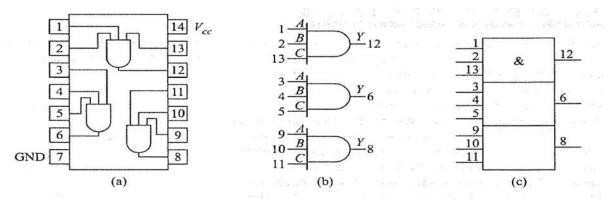

Triple three-input AND gate, 7 411: (a) Pin configuration, (b) Logic symbol,

(c) Logic symbol (IEEE)

The pin out and symbols for the 7411 quad 2-input. The new IEEE symbol for the AND gate is a rectangle with the ampersand (&) symbol written in it; is used in Fig. 1.37c to show the three AND gates in the 7411.

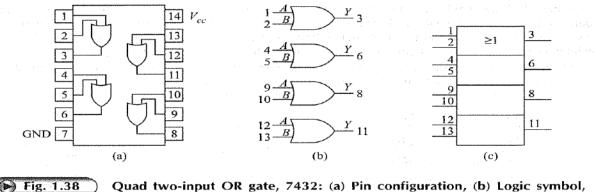

Quad two-input OR gate, 7432: (a) Pin configuration, (b) Logic symbol, (c) Logic symbol (IEEE)

### **DIGITAL LOGIC**

- A digital circuit having one or more input signals but only one output signal is called a *gate* .the most basic gates-the NOT gate (inverter), the OR gate and the AND gate-were introduced.

- Connecting the basic gates in different ways makes it possible to produce circuits that perform arithmetic and other functions associated with the human brain (an ALU). Because they simulate mental processes, gates are often called *logic circuits*.

A discussion of both positive and negative logic leads to the important concept of *assertion-/eve/ logic*.

Hardware description languages (HDL) are an alternative way of describing logic circuits. This uses a set of textual codes that is machine (computer) readable.

#### THE BASIC GATES-NOT, OR, AND

Three logic circuits: the *inverter*, the *OR gate*, and the *AND gate*, can be used to produce any digital system.

#### The Inverter (NOT Gate)

In one truth table, the symbols Hand *L* are used, while the binary numbers O and 1 are used .in the other. The information in each table is identical, however, since we know L = 0 and H = 1.

In this text, both symbols are used, hence since there is no chance for confusion. You will find both symbols used in other texts, as well as in manufacturers' data sheets.

- The important idea is that there are only two possible voltage levels (low and high) associated with a digital circuit. This fits nicely with the binary number system, since it has only two values (0 and 1). This is often referred to as *two-state operation*.

- By definition, this is *positive logic*, since the *higher* voltage level is assigned binary 1. In negative logic, where the *higher* voltage level is assigned binary (zero).

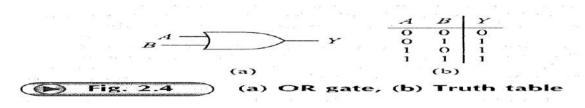

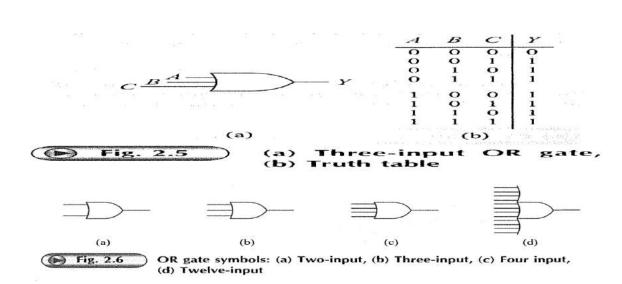

### **OR** Gates

An OR gate has two or more input signals but only one output signal. It is called an OR gate because the output voltage is high if any or all of the input voltages are high. For instance, the output of a 2-input OR gate is high if either or both inputs are high.

For example, the first ABC entry is 000, the next is 001, then 010, and so on, up to the final entry of 111. Since all binary numbers are present, all input possibilities are included.

- > Incidentally, the number of rows in a truth table equals 2", where *n* is the number of inputs. For a 2-input OR gate, the truth table has 22, or 4 rows. A 3-input OR gate has a truth table with  $2^3$ , or 8 rows, while a 4-input OR gate results in 24, or 16 rows, and so on.

- An OR gate can have as many inputs as desired. No matter how many inputs, the action of any OR gate is summarized like this: One or more high inputs produce a high output.

#### logic Symbols

- Figure 2.6a shows the symbol for a 2-input OR gate of any design. Whenever you see this symbol, remember the output is high if either input is high.

- The logic symbol for a 3-input OR gate. Figure 2.6c is the symbol for a 4-input OR gate. For these gates, the output is high when any input is high. The only way to get output allow is by having all inputs low.

- When there are many input signals, it's common drafting practice to extend the input side as needed to allow sufficient space between the input lines.

- It is the symbol for a 12-input OR gate. The same idea applies to any type of gate; extend the input side when necessary to accommodate a large number of input signals.

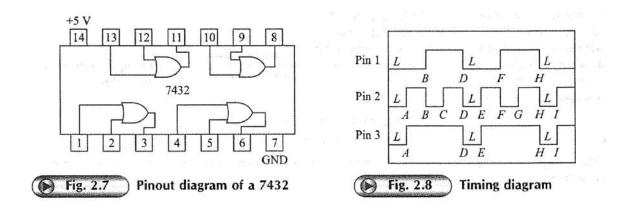

- TTL OR Gates Figure 2.7 shows the pinout diagram of a 7432, a TTL quad 2-input OR gate. This digital IC contains four 2-input OR gates inside a 14-pin DIP. After connecting a supply voltage of +5 V to pin 14 to and a ground pin 7, you can connect one or more of the OR gates to other TTL devices

Timing Diagram Figure 2.8 shows an example of a timing diagram for a 2-input OR gate. The input voltages drive pins 1 and 2 of7432a. Notice that the output (pin 3) is low only when both inputs are low. The output is high the rest of the time because one or more input pins are high.

### **AND Gates**

- The AND gate has a high output only when all inputs are high. Figure 2.1a shows a 2-input AND gate. The truth table (Fig. 2.10 b) summarizes all input-output possibilities for a 2-input AND gate.

- Examine this table carefully and remember the following: the AND gate has a high output only when *A* and *B* are high. In other words, the AND gate is an all-or-nothing gate; a high output occurs only when all inputs are high. This truth table uses 1s and 0s, where 1 = Hand 0 = L.

- > In Boolean equation form =A AND B, i.e. Y=A.B or Y=AB

- Y = 0.0 = 0, Y = 0.1 = 0, Y = 1.0 = 0 and Y = 1.1 = 1

- The '.' sign here represents logic AND operation and not multiplication operation of basic arithmetic though the result for are same both.

- TTL AND Gates Figure 2.13 shows the pinout diagram of a 7408, a TTL quad 2-input AND gate. This digital IC contains four 2-input AND gates.

- After connecting a supply voltage of +5V to pin 14 and a ground to pin 7, you can connect one or more of the AND gates to other TTL devices.

- > TTL AND gates are also available in triple 3-input and dual 4-input packages.

Timing Diagram Figure 2.14 shows an example of a timing diagram for a 2-input AND gate. The input voltages drive pins 1 and 2 of a 7408. Notice that the output (pin 3) is high only when both inputs are high (between C and D, G and H, etc.). The output is low the rest of the time.

#### **UNIVERSAL LOGIC GATES-NOR, NAND**

- Gates, which can perform this task, are called universal logic gates. Clearly, basic gates like AND, OR and NOT don't fit into this category for the simple reason that conversion among themselves itself are not possible. As for example, one cannot gate OR operation by using number any or combination of AND gates.

- ▶ Two universal logic gates NOR and NAND.

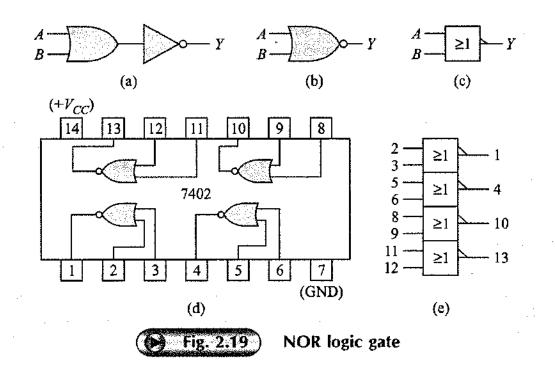

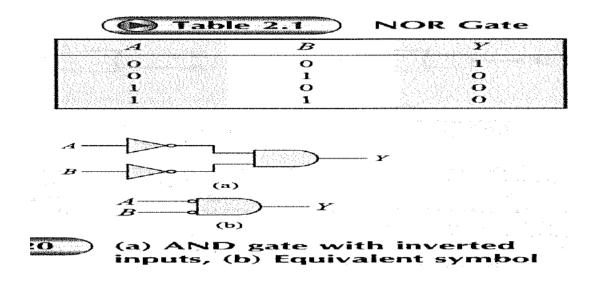

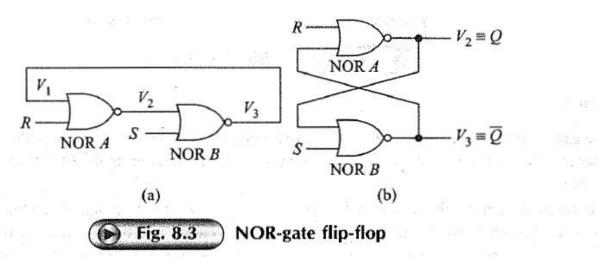

### **NOR Gates**

> The logic circuit used to be called a NOT-OR gate because the output is

#### Y = A + B

Read this as "Y equals NOT A OR B" or "Y equals the complement of A OR B." Because the circuit is an OR gate followed by an inverter, the only way to get a high output is to have both inputs low, as shown in the truth table of Table 2.1.

#### **NOR Gate Symbol**

The bubble (small circle) on the output is a reminder of the inversion that takes place after the ORing. Furthermore, the words NOT-OR are contracted to the word NOR.

## NOR logic gate

➤ The new IEEE rectangular symbol for the NOR gate. The small triangle on the output is equivalent to the bubble used on the standard symbol. The indicator ≥ inside the box means "if one or more of the inputs are high, the output is high."

#### **Bubbled AND Gate**

- The bubbles on the inputs are a reminder of the inversion that takes place before the AND operation. It is *bubbled AND gate*. We find that output *Y* and inputs *A*, *B* are identical for bubbled AND gate and NOR gate.

- Therefore, these two circuits and are equivalent thus interchangeable. Given any logic circuit with NOR gates, we can replace it by bubbled AND gates and converse is also true.

#### **De Morgan'sFirst Theorem**

The Boolean equation for Fig. 2.19b is Y=A+B

The Boolean equation for Fig. 2.20b is Y=AB

The first equation describes a NOR gate, and the second equation a bubbled AND gate. Since the outputs same inputs, we can equate the right~hand members to get.

$$\overline{A+B} = \overline{A}\,\overline{B}$$

This identity is known as De Morgan'sFirst Theorem. In words, it says the complement of a sum equals the product of the complements. This can also be proved by comparing the truth tables shown in Fig. 2.4(b) and NOR gate truth table of Table 2.1. A similar exercise that compares truth tables of three input NOR gate and three input bubbled AND gate show they are identical and we can write, (A+B+C)' = A'B'C'. Note that this equivalence can be extended to gates or circuits for larger number of inputs, too.

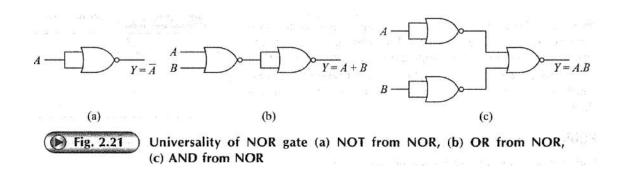

#### **Universality of NOR Gate**

Figure 2.21 shows how all other logic gates can be obtained from NOR gates. To get a NOT gate we tie inputs of NOR gate together (Fig. 2.21 a) so that there is only one input to the circuit. If input is 0, then both

The inputs to NOR gate are 0. Following NOR gate truth table (Table 2see.1) we output now is 1. Similarly, if input is 1, both the inputs to NOR gate are 1 that gives output 0. Therefore output of circuit, shown in Fig. 2.2 la is complement of its input and thus gives NOT operation.

#### Eye of the Beholder

Truth tables, logic circuits, and Boolean equations are different ways of looking at the same thing. Whatever we learn from one viewpoint applies to the other two. If we prove that truth tables are identical, this immediately tells us the corresponding logic circuits are interchangeable, and their Boolean equations are equivalent.

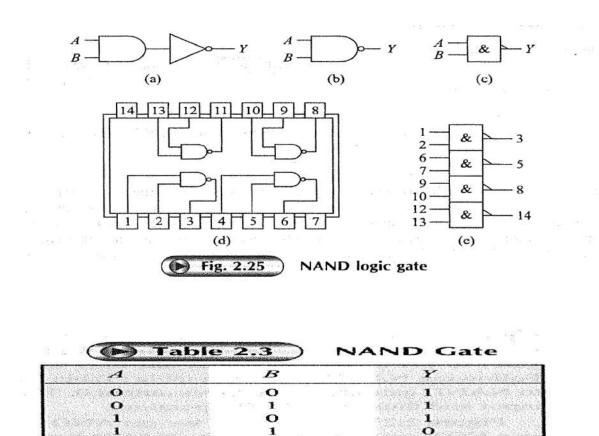

## NAND Gates

- > Originally, the logic circuit was called NOT-AND gate because the output is Y=AB

- Read this as "Y equals NOT A AND B" or "Y equals the complement of A AND B." Because the circuit is an AND gate followed the by an inverter, only way to get a low output is for both inputs to be high, as shown in the truth table of Table.

#### **NAND-Gate Symbol**

- The logic circuit has become so popular that the abbreviated symbol is used for it. The bubble on the output reminds us of the inversion after the ANDing.

- Also, the words NOT-AND are contracted to NAND. Whenever you see this symbol, remember that the output is NOT the AND of the inputs. With a NAND gate, all inputs must be high to get a low output. If any input is low, the output is high.

- The new IEEE rectangular symbol for the NAND gate. The small triangle on the output is equivalent to the bubble used on the standard symbol. The indicator"&" inside the box means "the output is high only when *all* inputs are high."

## **Bubbled OR Gate**

Inverters on the input lines of an OR gate. The circuit is often drawn in the abbreviated form, where the bubbles represent inversion. We will refer to the abbreviated drawing of as a *bubbled* OR gate.

#### **De Morgan'sSecond Theorem**

The Boolean equation for Y=ABThe Boolean equation for Y=X+B

The first equation describes a NAND gate, and the second equation a bubbled OR gate. Since the outputs are equal for the same inputs, we can equate the right-hand members to get

$$A = A + B \qquad 2.2)$$

- This identity is known as *De Morgans second theorem*. It says the complement of a product equals the sum of the complements. This can also be proved by comparing the truth tables shown in Fig. 2.3(b) and NAND gate truth table of Table 2.2.

- A similar exercise that compares truth tables of three input NAND gate and three input bubbled OR gate show they are identical and we can write, (A.B.C)' = A' + B' + C'. Note that this equivalence can be extended to gates or circuits with any number of inputs.

#### **Universality of NANO Gate**

- How all other logic gates can be obtained from NAND gates and why it is called a universal logic gate. Figure 2.27a shows how we tie inputs of NAND gate together (as we had done in case of NOR gate) to get a NOT gate that has only one input.

- If input is 0, then both the inputs to NAND gate are. 0. Following NAND gate trnth table (Table 2.3) we see output now isl. Similarly, if input is 1, both the inputs to NAND gate are 1 that gives output 0. Therefore output of circuit, shown in Fig. 2.27a is complement of its input and thus gives NOT operation.

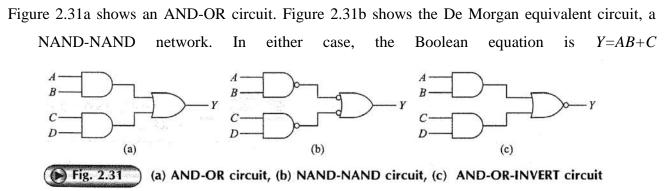

#### 2.3 AND-OR-INVERT GATES

Since NAND gates are the preferred TTL gates, we would build the circuit of Fig. 2.31 b. As you know, NAND-NAND circuits like this are important because with them you can build any desired logic circuit.

#### **TTL Devices**

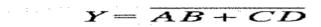

AND-OR circuits are not easily derived from the basic NAND-gate design. But it is easy to get an AND-OR-INVERT circuit as in Fig. 2.3 lc. A variety of circuits like this are available as TTL chips. Because of the inversion, the output has the equation shown below.

- Table 2.6 lists the AND-OR-INVERT gates available in the 7400 series. In this table, 2-wide means two AND gates across, 4-wide means four AND gates across, and so on.

- For instance, the 7454 is a 2-input 4-wide AND-OR-INVERT gate ; each AND gate has two inputs (2-input), and there are four AND gates (4-wide). Figure 2.32b shows the 7464; it is a 2-2-3-4-input 4-wide AND-OR-INVERT gate.

| Table 2.6 | AND-OR-INVERT Gate    |  |

|-----------|-----------------------|--|

| Device    | Description           |  |

| 7451      | Dual 2-input 2-wide   |  |

| 7454      | 2-input 4-wide        |  |

| 7459      | Dual 2-3-input 2-wide |  |

| 7464      | 2-2-3-4-input 4-wide  |  |

Connecting the output of a 2-input 2-wide AND-OR-INVERT gate to an inverter will give us the same output as an AND-OR circuit.

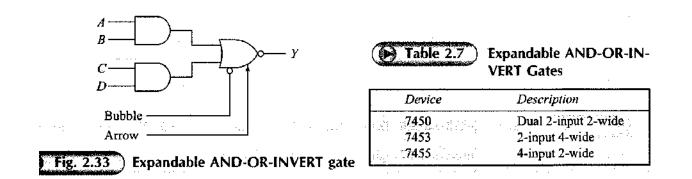

### **Expandable AND-OR-INVERT Gates**

- The widest AND-OR-INVERT gate available in the 7400 series is 4-wide. What do we do when we need a 6- or 8-wide circuit? One solution is to use an *expandable* AND-OR-INVERT gate.

- Figure 2.33 shows the logic symbol for an expandable AND-OR-INVERT gate. There are two additional inputs, labeled *bubble* and *arrow*. Table 2.7 lists the expandable AND-OR-INVERT gates in the 7400 series.

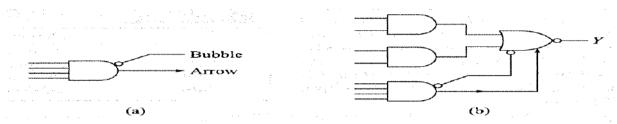

#### Expanders

- Connect bubble to bubble and arrow to arrow.

- Visualize the outputs of Fig. 2.34a connected to the arrow and bubble inputs of Fig. 2.33. Figure 2.34b shows the logic circuit. This means that the expander outputs are being ORed with the

signals of the AND-OR-INVERT gate. In other words, Fig. 2.34b is equivalent to the AND-OR-INVERT circuit of Fig. 2.34c.

- We can connect Figure more expanders. It shows two expanders driving the expandable gate. Now we have a 2-2-4-4-input 4-wide AND-OR-INVERT circuit.

- The 7460 is a dual 4-input expander. The 7450, a dual expandable AND-OR-INVERT gate, is designed for use with up to four 7460 expanders. This means that we can add two more expanders in Fig. 2-34d to get a 2-2-4-4-4-input 6-wide AND-OR-INVERT circuit.

## **POSITIVE AND NEGATIVE LOGIC**

- Up to now, we have used a binary O for low voltage and a binary 1 for high voltage. This is called *positive logic*.

- People are comfortable with positive logic because it feels right. But there is another code known as *negative logic* where binary O stands for high voltage and binary 1 for low voltage. Even though it seems unnatural, negative logic has many uses.

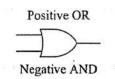

### **Positive and Negative Gates**

An OR gate in a positive logic an system becomes AND gate in a negative logic system. That is, if either input is high in Fig. 2.35, the output is high.

| A    | B    | Y    |  |  |

|------|------|------|--|--|

| Low  | Low  | Low  |  |  |

| Low  | High | High |  |  |

| High | Low  | High |  |  |

| High | High | High |  |  |

( > Table 2.8 )

Meaning of symbol depends on whether you use positive or negative logic

- In a positive logic system, binary O stands for low and binary 1 for high. So, we can convert Table 2.8 to Table 2.9. Note that Y is a 1 if either A or B is 1. This sounds like an OR gate.

- And it is, because we are using positive logic. To avoid ambiguity, a positive OR gate because it performs the OR function with positive logic. (Some data sheets describe gates as positive OR gate, positive AND gate, etc.)

- ➢ In a negative logic system, binary 1 stands for low and binary O for high. With this code. Now, watch what happens. The output *Y* is a 1 only when both *A* and *B* are 1.

- This sounds like an AND gate! And it is, because we are now using negative logic. In other words, gates are defined by the way they process the binary Os and 1s. If you use binary 1 for low voltage and binary O for high voltage, then you liave to refer to Fig. 2.35 as a negative AND gate.

|        | D Table |          |          | - |   | Table 2  | and the second se |

|--------|---------|----------|----------|---|---|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A 10-5 | В       | Y - (* ) |          |   | A | <i>B</i> | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0      | 0       | 0        | n (c. 11 |   | 1 | 1        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0      | 1       | 1        |          |   | 1 | 0        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1      | 0       | $1^{-1}$ |          |   | 0 | 1        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1      | 1       | 1        |          |   | 0 | 0        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

In a similar way, we can show the truth table of other gates with positive or negative logic. By analyzing the inputs and outputs in terms of Os and ls, you find these equivalences between the positive and negative logic:

| Positive OR   | $\leftrightarrow$ negative AND  |

|---------------|---------------------------------|

| Positive AND  | $\leftrightarrow$ negative OR   |

| Positive NOR  | $\leftrightarrow$ negative NAND |

| Positive NAND | $\leftrightarrow$ negative NOR  |

|               |                                 |

These definitions are always valid. If you get confused from time to time, refer to Table 2.11 to get back to the ultimate meaning of the basic gates.

| Gate                       | Definition                               |  |

|----------------------------|------------------------------------------|--|

| Positive OR/negative AND   | Output is high if any input is high.     |  |

| Positive AND/negative OR   | Output is high when all inputs are high. |  |

| Positive NOR/negative NAND | Output is low if any input is high.      |  |

| Positive NAND/negative NOR | Output is low when all inputs are high.  |  |

Voltage Definitions of Pasis Cate

## Assertion-level logic

- Why do we even bother with negative logic? The reason is related to the concept of *active-low signals*. For instance, the 74150 multiplexer has an active-low input strobe; this input turns on the chip only when it is low (negative true).

- This is an active-low signal; it causes something to happen when it is low, rather than high. As another example, the 74154 decoder has 16 output lines; the decoded output signal is low (negative true).

- In other words, all output lines have a high voltage, except the decoded output line. Besides TTL devices, microprocessor chips like the 8085 have a lot of active-low input and output signals.

- Many designers draw their logic circuits with bubbles on all pins with active-low signals and omit bubbles on all pins with active-high signals. This use of bubbles with active-low signals is called *assertion-level logic* that.

- It means you draw chips with the kind of input that causes something to happen, or with the kind of output that indicates something has happened. If a low input signal turns on a chip, you show a bubble on that input.

- If a low output is a sign of chip action, you draw a bubble on that output. Once you get used to assertion-level you may prefer drawing logic circuits this way.

- Sometimes you hear expressions such as "The inputs are asserted" or "What happens when the inputs are asserted?" An input is *asserted* when it is active. This means it may be low or high, depending on whether it is an active-low or active-high input.

- For instance, given a positive AND gate, all inputs must be asserted (high) to get a high output. As another example, the STROBE input of a TTL multiplexer must be asserted (low) to turn on

the multiplexer. In short, you can equate the word *assert* with *activate*. You assert, or activate, the inputs of a gate or device to get something to happen.

## <u>UNIT -II</u>

# **COMBINATIONAL LOGIC CIRCUIT**

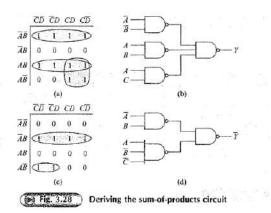

- This chapter discusses Boolean algebra and several simplification techniques. After learning the laws and theorems of Boolean algebra, you can rearrange Boolean equations to arrive at simpler logic circuits.

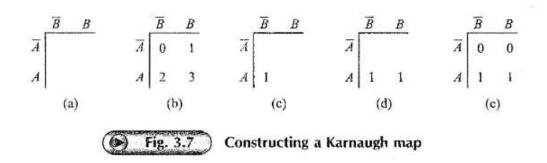

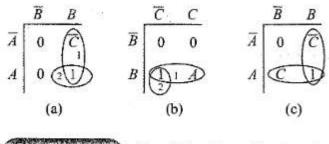

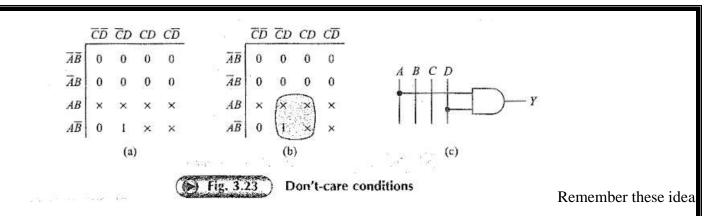

- An alternative method of simplification is based on the Kanaugh map. In this approach, geometric rather than algebraic techniques are used to simplify logic circuits.

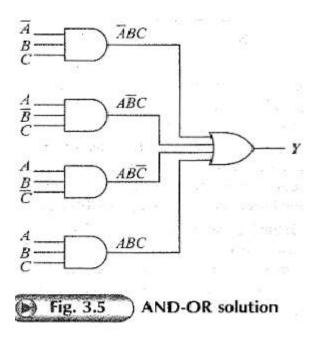

- Quine-McClusky tabular method provides a more systematic reduction technique, which is preferred when a large number of variables are in consideration. There are two fundamental approaches in logic design:

- 1. The sum-of-products method

- 2. product-of sum method

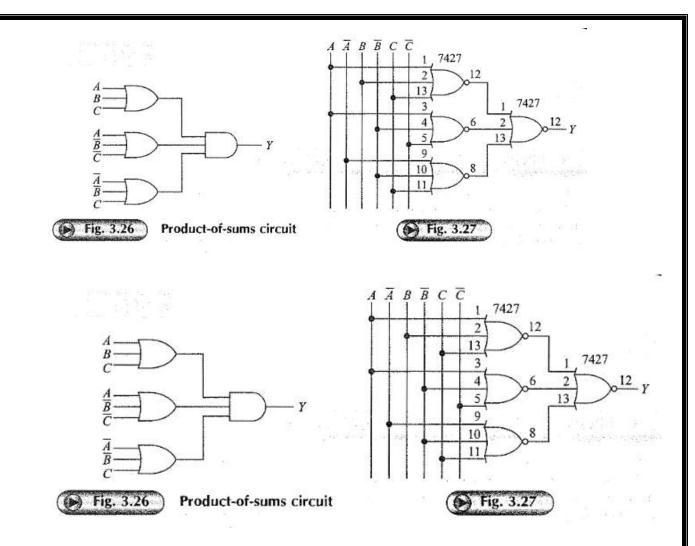

- > The sum-of-products solution results in an AND-OR or NAND-NAND network,

- ▶ while the product-of-sums solution results in an OR-AND or NOR-NOR network.

## **BOOLEAN LAWS & THEOREMS**

### **Basic laws**

The commutative laws are

| A + B = B + A |  | (3.1) |

|---------------|--|-------|

| AB = BA       |  | (3.2) |

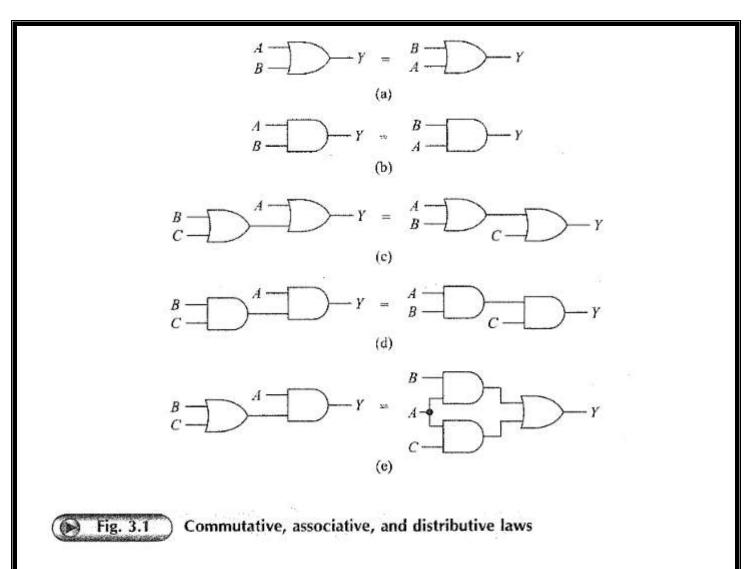

- These two equations indicate that the order of a logical operation is unimportant because the same answer is arrived at either way. As far as logic circuits are concerned. Figure 3.la shows how to visualize Eq. (,.1).

- All it amounts to is realizing that the inputs to an OR gate can be transposed without changing the output. Likewise, Fig. 3.lb is a graphical equivalent for Eq. (3.2).

The associative laws are

$$A + (B + C) = (A + B) + C$$

(3.3)

$A(BC) = (AB)C$  (3.4)

These laws show that the order of combining variables has no effect on the final answer. In terms of logic circuits, Eq Fig. 3.1c (3.3) while 3.1d represents illustrates Eq. (3.4).

The distribute law is

$$A(B+C) = AB + AC$$

- This law is easy to remember because it is identical to ordinary algebra. Figure 3 .1 e shows the corresponding logic equivalence. The distributive law gives you a hint about the value of Boolean algebra.

- If you can rearrange a Boolean expression, the corresponding logic circuit may be simpler.

- The first five laws present no difficulties because they are identical to ordinary algebra. You can use these laws to simplify complicated and Boolean expressions arrive at simpler logic circuits.

- But before you begin, you have to learn other Boolean laws and theorems.

### **OR** Operations

The next four Boolean relations are about OR operations. Here is the first:

A+O=A

This says that a variable ORed with O equals the variable. If you think about it, makes perfect sense. When A is 0,

0+0 =0

And when A is 1,

```

1 + 0 = 1

```

In either Eq. case, (3.6) is true.

Another Boolean relation is

A + A = A

Again, you can see right through this by substituting the two possible values of *A*. First when A = 0, Eq.(3.7) gives

$$O = O + O$$

which is true. Next, A = I results in

$$1 + 1 = 1$$

which is also true because 1 ORed with 1 produces 1. Therefore, any variable ORed with itself equals the variable.

Another Boolean rule worth knowing is

A + I = 1

Why is this valid? When A = 0, Eq. (3.8) gives

0 + 1 = 1

which is true. Also, A = 1 gives

1 + 1 = 1

This is correct because the plus sign implies OR addition, not ordinary addition. In summary,

The next four Boolean relations are about OR operations. Here is the first:

A + O = A

This says that a variable ORed with O equals the variable. If you think about it, makes perfect sense. When A is 0,

$$O+O=O$$

And when A is 1,

1 + 0 = 1

In either Eq. case, (3.6) is true.

Another Boolean relation is

A + A = A

Again, you can see right through this by substituting the two possible values of *A*. First when A = 0, Eq.

$(3.7) gives \qquad O+O=O$

which is true. Next, A = I results in

1 + 1 = 1

The next four Boolean relations are about OR operations. Here is the first:

A+O=A

This says that a variable ORed with O equals the variable. If you think about it, makes perfect sense. When A is 0,

```

O+O =O

```

And when A is 1,

1 + 0 = 1

In either Eq. case, (3.6) is true.

Another Boolean relation is

A + A = A

Again, you can see right through this by substituting the two possible values of

A. First when A = 0, Eq.

(3.7) gives

which is true. Next, A = I results in

$$1 + 1 = 1$$

This is correct because the plus sign implies OR addition, not ordinary addition. In summary,

Eq. (3.8) says this, input if one to an OR gate is high, the output is high no matter what the other input.

Finally, we have

### A + A = I

You should see this in a flash. If A is 0, A is 1 and the equation is true. Conversely if A is 1, A is 0 and The equation agree still. In short , a variable Red with its complement always equals 1.

## **AND Operations**

Here are three AND relations

$$A \cdot 1 = A$$

$A \cdot A = A$

$A \cdot O = O$

When A is 0, all the foregoing are true. Likewise, when A is 1, each is true.

Therefore, the three equations

are valid and can be used to simplify Boolean equations.

One more AND formula is

$A \cdot A = O$

This one easy to understand because you get either

$0 \cdot 1 = 0$

or

$$\mathbf{I} \cdot \mathbf{0} = \mathbf{0}$$

for the two possible values of A. In words, Eq. (3.13) indicates that a variable ANDed with its complement always equals zero.

**Double Inversion and De Morgan's Theorems**

The double-inversion nde is

$$A = A$$

which shows that the double complement of a variable equals the variable. Finally, there are the De Morgan theorems discussed in Chapter 2:

| A + B = AB | (3.15) |

|------------|--------|

|            |        |

$AB = A + B \tag{3.16}$

You already know how important these are. The first says a NOR gate and a bubbled AND gate are equivalent. The second says a NAND gate and a bubbled OR gate are equivalent.

## **Duality Theorem**

The *duality theorem* is one of those elegant theorems proved in advanced mathematics. We will state the theorem without proof. Here is what the duality theorem says. Starting with a Boolean relation, you can derive another Boolean relation by

Changing each OR sign to an AND sign

Changing each AND sign to an OR sign

➤ Complementing any O or 1 appearing in the expression

For instance, Eq. (3.6) says that

A + O = A

The dual relation is

### $A \cdot 1 = A$

This dual property is obtained by changing the OR sign to an AND sign, and by complementing the O to get a 1.

The duality theorem is useful because it sometimes produces a new Boolean relation. For example, Eq. (3.5) states that

$$A(B+C) = AB+AC$$

By changing each OR and AND operation, we get relation the dual

$$A + BC = (A + B)(A + C)$$

# **Covering and Combination**